16-Bit Core Instruction Set

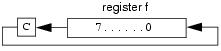

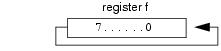

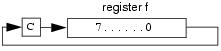

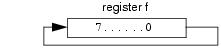

Microchip's high-performance 8-bit microcontroller family uses a 16-bit wide instruction set. This instruction set consists of 55 instructions, each a single 16-bit wide word. Most instructions operate on a file register, f, and the working register, WREG (accumulator). The result can be directed either to the file register or the WREG register or to both in the case of some instructions. Some devices in this family also include hardware multiply instructions. A few instructions operate solely on a file register (BSF for example).

The instruction set is grouped into the following catagories: Byte-oriented file register operations, bit-oriented file register operations, and core literal and control operations. Instructions are listed by catagory in the tables below. Instruction opcode is show in Hex by certain making assumptions, either listed in the key or as a footnote. For more information on the opcode bit values for each instruction, as well as the number of cycles per instruction, status bits affected and complete instruction details, see the relevent device data sheet.

|

Microchip Technology Inc. Microchip's Web Site Voice: (480) 792-7200 Fax: (480) 899-9210 Microchip's E-mail Address |

|