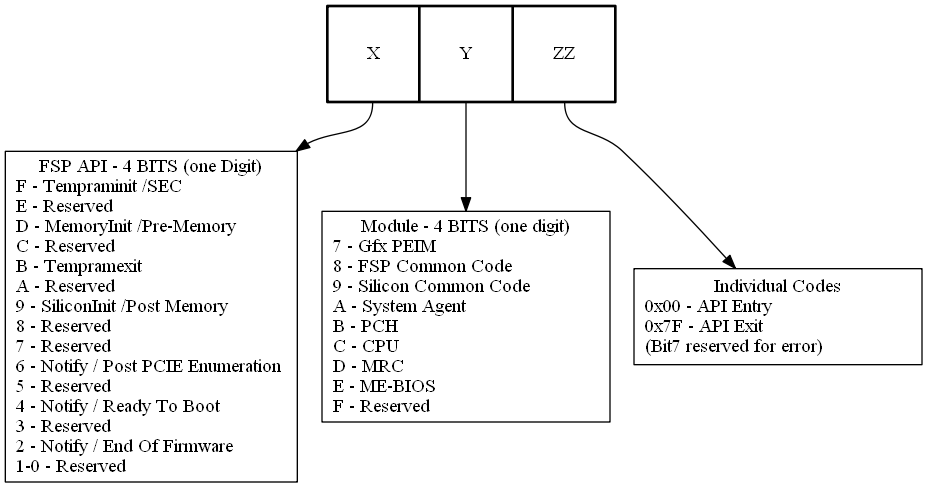

The FSP outputs 16 bit postcode to indicate which API and in which module the execution is happening.

Below diagram represents the 16 bit PostCode usage in FSP.

| PostCode | Module | Description |

| 0xD800 | FSP | FspMemoryInit API Entry |

| 0xD87F | FSP | FSpMemoryInit API Exit |

| 0xDA00 | SA | Pre-Mem SaInit Entry |

| 0xDA02 | SA | OverrideDev0Did Start |

| 0xDA04 | SA | OverrideDev2Did Start |

| 0xDA06 | SA | Programming SA Bars |

| 0xDA08 | SA | Install SA HOBs |

| 0xDA0A | SA | Reporting SA PCIe code version |

| 0xDA0C | SA | SaSvInit Start |

| 0xDA10 | SA | Initializing DMI |

| 0xDA15 | SA | Initialize TCSS PreMem |

| 0xDA1F | SA | Initializing DMI/OPI Max PayLoad Size |

| 0xDA20 | SA | Initializing SwitchableGraphics |

| 0xDA30 | SA | Initializing SA PCIe |

| 0xDA3F | SA | Programming PEG credit values Start |

| 0xDA40 | SA | Initializing DMI Tc/Vc mapping |

| 0xDA42 | SA | CheckOffboardPcieVga |

| 0xDA44 | SA | CheckAndInitializePegVga |

| 0xDA50 | SA | Initializing Graphics |

| 0xDA52 | SA | Initializing System Agent Overclocking |

| 0xDA7F | SA | Pre-Mem SaInit Exit |

| 0xDB00 | PCH | Pre-Mem PchInit Entry |

| 0xDB02 | PCH | Pre-Mem Disable PCH fused controllers |

| 0xDB15 | PCH | Pre-Mem SMBUS configuration |

| 0xDB48 | PCH | Pre-Mem PchOnPolicyInstalled Entry |

| 0xDB49 | PCH | Pre-Mem Program HSIO |

| 0xDB4A | PCH | Pre-Mem DCI configuration |

| 0xDB4C | PCH | Pre-Mem Host DCI enabled |

| 0xDB4D | PCH | Pre-Mem Trace Hub - Early configuration |

| 0xDB4E | PCH | Pre-Mem Trace Hub - Device disabled |

| 0xDB4F | PCH | Pre-Mem TraceHub - Programming MSR |

| 0xDB50 | PCH | Pre-Mem Trace Hub - Power gating configuration |

| 0xDB51 | PCH | Pre-Mem Trace Hub - Power gating Trace Hub device and locking HSWPGCR1 register |

| 0xDB52 | PCH | Pre-Mem Initialize HPET timer |

| 0xDB55 | PCH | Pre-Mem PchOnPolicyInstalled Exit |

| 0xDB7F | PCH | Pre-Mem PchInit Exit |

| 0xDC00 | CPU | CPU Pre-Mem Entry |

| 0xDC0F | CPU | CpuAddPreMemConfigBlocks Done |

| 0xDC20 | CPU | CpuOnPolicyInstalled Start |

| 0xDC2F | CPU | XmmInit Start |

| 0xDC3F | CPU | TxtInit Start |

| 0xDC4F | CPU | Init CPU Straps |

| 0xDC5F | CPU | Init Overclocking |

| 0xDC6F | CPU | CPU Pre-Mem Exit |

| 0x**55 | SA | MRC_MEM_INIT_DONE |

| 0x**D5 | SA | MRC_MEM_INIT_DONE_WITH_ERRORS |

| 0xDD00 | SA | MRC_INITIALIZATION_START |

| 0xDD10 | SA | MRC_CMD_PLOT_2D |

| 0xDD1B | SA | MRC_FAST_BOOT_PERMITTED |

| 0xDD1C | SA | MRC_RESTORE_NON_TRAINING |

| 0xDD1D | SA | MRC_PRINT_INPUT_PARAMS |

| 0xDD1E | SA | MRC_SET_OVERRIDES_PSPD |

| 0xDD20 | SA | MRC_SPD_PROCESSING |

| 0xDD21 | SA | MRC_SET_OVERRIDES |

| 0xDD22 | SA | MRC_MC_CAPABILITY |

| 0xDD23 | SA | MRC_MC_CONFIG |

| 0xDD24 | SA | MRC_MC_MEMORY_MAP |

| 0xDD25 | SA | MRC_JEDEC_INIT_LPDDR3 |

| 0xDD26 | SA | MRC_RESET_SEQUENCE |

| 0xDD27 | SA | MRC_PRE_TRAINING |

| 0xDD28 | SA | MRC_EARLY_COMMAND |

| 0xDD29 | SA | MRC_SENSE_AMP_OFFSET |

| 0xDD2A | SA | MRC_READ_MPR |

| 0xDD2B | SA | MRC_RECEIVE_ENABLE |

| 0xDD2C | SA | MRC_JEDEC_WRITE_LEVELING |

| 0xDD2D | SA | MRC_LPDDR_LATENCY_SET_B |

| 0xDD2E | SA | MRC_WRITE_TIMING_1D |

| 0xDD2F | SA | MRC_READ_TIMING_1D |

| 0xDD30 | SA | MRC_DIMM_ODT |

| 0xDD31 | SA | MRC_EARLY_WRITE_TIMING_2D |

| 0xDD32 | SA | MRC_WRITE_DS |

| 0xDD33 | SA | MRC_WRITE_EQ |

| 0xDD34 | SA | MRC_EARLY_READ_TIMING_2D |

| 0xDD35 | SA | MRC_READ_ODT |

| 0xDD36 | SA | MRC_READ_EQ |

| 0xDD37 | SA | MRC_READ_AMP_POWER |

| 0xDD38 | SA | MRC_WRITE_TIMING_2D |

| 0xDD39 | SA | MRC_READ_TIMING_2D |

| 0xDD3A | SA | MRC_CMD_VREF |

| 0xDD3B | SA | MRC_WRITE_VREF_2D |

| 0xDD3C | SA | MRC_READ_VREF_2D |

| 0xDD3D | SA | MRC_POST_TRAINING |

| 0xDD3E | SA | MRC_LATE_COMMAND |

| 0xDD3F | SA | MRC_ROUND_TRIP_LAT |

| 0xDD40 | SA | MRC_TURN_AROUND |

| 0xDD41 | SA | MRC_CMP_OPT |

| 0xDD42 | SA | MRC_SAVE_MC_VALUES |

| 0xDD43 | SA | MRC_RESTORE_TRAINING |

| 0xDD44 | SA | MRC_RMT_TOOL |

| 0xDD45 | SA | MRC_WRITE_SR |

| 0xDD46 | SA | MRC_DIMM_RON |

| 0xDD47 | SA | MRC_RCVEN_TIMING_1D |

| 0xDD48 | SA | MRC_MR_FILL |

| 0xDD49 | SA | MRC_PWR_MTR |

| 0xDD4A | SA | MRC_DDR4_MAPPING |

| 0xDD4B | SA | MRC_WRITE_VOLTAGE_1D |

| 0xDD4C | SA | MRC_EARLY_RDMPR_TIMING_2D |

| 0xDD4D | SA | MRC_FORCE_OLTM |

| 0xDD50 | SA | MRC_MC_ACTIVATE |

| 0xDD51 | SA | MRC_RH_PREVENTION |

| 0xDD52 | SA | MRC_GET_MRC_DATA |

| 0xDD53 | SA | Reserved |

| 0xDD58 | SA | MRC_RETRAIN_CHECK |

| 0xDD5A | SA | MRC_SA_GV_SWITCH |

| 0xDD5B | SA | MRC_ALIAS_CHECK |

| 0xDD5C | SA | MRC_ECC_CLEAN_START |

| 0xDD5D | SA | MRC_DONE |

| 0xDD5F | SA | MRC_CPGC_MEMORY_TEST |

| 0xDD60 | SA | MRC_TXT_ALIAS_CHECK |

| 0xDD61 | SA | MRC_ENG_PERF_GAIN |

| 0xDD68 | SA | MRC_MEMORY_TEST |

| 0xDD69 | SA | MRC_FILL_RMT_STRUCTURE |

| 0xDD70 | SA | MRC_SELF_REFRESH_EXIT |

| 0xDD71 | SA | MRC_NORMAL_MODE |

| 0xDD7D | SA | MRC_SSA_PRE_STOP_POINT |

| 0xDD7F | SA | MRC_SSA_STOP_POINT, MRC_INITIALIZATION_END |

| 0xDD90 | SA | MRC_CMD_PLOT_2D_ERROR |

| 0xDD9B | SA | MRC_FAST_BOOT_PERMITTED_ERROR |

| 0xDD9C | SA | MRC_RESTORE_NON_TRAINING_ERROR |

| 0xDD9D | SA | MRC_PRINT_INPUT_PARAMS_ERROR |

| 0xDD9E | SA | MRC_SET_OVERRIDES_PSPD_ERROR |

| 0xDDA0 | SA | MRC_SPD_PROCESSING_ERROR |

| 0xDDA1 | SA | MRC_SET_OVERRIDES_ERROR |

| 0xDDA2 | SA | MRC_MC_CAPABILITY_ERROR |

| 0xDDA3 | SA | MRC_MC_CONFIG_ERROR |

| 0xDDA4 | SA | MRC_MC_MEMORY_MAP_ERROR |

| 0xDDA5 | SA | MRC_JEDEC_INIT_LPDDR3_ERROR |

| 0xDDA6 | SA | MRC_RESET_ERROR |

| 0xDDA7 | SA | MRC_PRE_TRAINING_ERROR |

| 0xDDA8 | SA | MRC_EARLY_COMMAND_ERROR |

| 0xDDA9 | SA | MRC_SENSE_AMP_OFFSET_ERROR |

| 0xDDAA | SA | MRC_READ_MPR_ERROR |

| 0xDDAB | SA | MRC_RECEIVE_ENABLE_ERROR |

| 0xDDAC | SA | MRC_JEDEC_WRITE_LEVELING_ERROR |

| 0xDDAD | SA | MRC_LPDDR_LATENCY_SET_B_ERROR |

| 0xDDAE | SA | MRC_WRITE_TIMING_1D_ERROR |

| 0xDDAF | SA | MRC_READ_TIMING_1D_ERROR |

| 0xDDB0 | SA | MRC_DIMM_ODT_ERROR |

| 0xDDB1 | SA | MRC_EARLY_WRITE_TIMING_ERROR |

| 0xDDB2 | SA | MRC_WRITE_DS_ERROR |

| 0xDDB3 | SA | MRC_WRITE_EQ_ERROR |

| 0xDDB4 | SA | MRC_EARLY_READ_TIMING_ERROR |

| 0xDDB5 | SA | MRC_READ_ODT_ERROR |

| 0xDDB6 | SA | MRC_READ_EQ_ERROR |

| 0xDDB7 | SA | MRC_READ_AMP_POWER_ERROR |

| 0xDDB8 | SA | MRC_WRITE_TIMING_2D_ERROR |

| 0xDDB9 | SA | MRC_READ_TIMING_2D_ERROR |

| 0xDDBA | SA | MRC_CMD_VREF_ERROR |

| 0xDDBB | SA | MRC_WRITE_VREF_2D_ERROR |

| 0xDDBC | SA | MRC_READ_VREF_2D_ERROR |

| 0xDDBD | SA | MRC_POST_TRAINING_ERROR |

| 0xDDBE | SA | MRC_LATE_COMMAND_ERROR |

| 0xDDBF | SA | MRC_ROUND_TRIP_LAT_ERROR |

| 0xDDC0 | SA | MRC_TURN_AROUND_ERROR |

| 0xDDC1 | SA | MRC_CMP_OPT_ERROR |

| 0xDDC2 | SA | MRC_SAVE_MC_VALUES_ERROR |

| 0xDDC3 | SA | MRC_RESTORE_TRAINING_ERROR |

| 0xDDC4 | SA | MRC_RMT_TOOL_ERROR |

| 0xDDC5 | SA | MRC_WRITE_SR_ERROR |

| 0xDDC6 | SA | MRC_DIMM_RON_ERROR |

| 0xDDC7 | SA | MRC_RCVEN_TIMING_1D_ERROR |

| 0xDDC8 | SA | MRC_MR_FILL_ERROR |

| 0xDDC9 | SA | MRC_PWR_MTR_ERROR |

| 0xDDCA | SA | MRC_DDR4_MAPPING_ERROR |

| 0xDDCB | SA | MRC_WRITE_VOLTAGE_1D_ERROR |

| 0xDDCC | SA | MRC_EARLY_RDMPR_TIMING_2D_ERROR |

| 0xDDCD | SA | MRC_FORCE_OLTM_ERROR |

| 0xDDD0 | SA | MRC_MC_ACTIVATE_ERROR |

| 0xDDD1 | SA | MRC_RH_PREVENTION_ERROR |

| 0xDDD2 | SA | MRC_GET_MRC_DATA_ERROR |

| 0xDDD3 | SA | Reserved |

| 0xDDD8 | SA | MRC_RETRAIN_CHECK_ERROR |

| 0xDDDA | SA | MRC_SA_GV_SWITCH_ERROR |

| 0xDDDB | SA | MRC_ALIAS_CHECK_ERROR |

| 0xDDDC | SA | MRC_ECC_CLEAN_ERROR |

| 0xDDDD | SA | MRC_DONE_WITH_ERROR |

| 0xDDDF | SA | MRC_CPGC_MEMORY_TEST_ERROR |

| 0xDDE0 | SA | MRC_TXT_ALIAS_CHECK_ERROR |

| 0xDDE1 | SA | MRC_ENG_PERF_GAIN_ERROR |

| 0xDDE8 | SA | MRC_MEMORY_TEST_ERROR |

| 0xDDE9 | SA | MRC_FILL_RMT_STRUCTURE_ERROR |

| 0xDDF0 | SA | MRC_SELF_REFRESH_EXIT_ERROR |

| 0xDDF1 | SA | MRC_MRC_NORMAL_MODE_ERROR |

| 0xDDFD | SA | MRC_SSA_PRE_STOP_POINT_ERROR |

| 0xDDFE | SA | MRC_NO_MEMORY_DETECTED |

| PostCode | Module | Description |

| 0x9800 | FSP | FspSiliconInit API Entry |

| 0x987F | FSP | FspSiliconInit API Exit |

| 0x9A00 | SA | PostMem SaInit Entry |

| 0x9A01 | SA | DeviceConfigure Start |

| 0x9A02 | SA | UpdateSaHobPostMem Start |

| 0x9A03 | SA | Initializing Pei Display |

| 0x9A04 | SA | PeiGraphicsNotifyCallback Entry |

| 0x9A05 | SA | CallPpiAndFillFrameBuffer |

| 0x9A06 | SA | GraphicsPpiInit |

| 0x9A07 | SA | GraphicsPpiGetMode |

| 0x9A08 | SA | FillFrameBufferAndShowLogo |

| 0x9A0F | SA | PeiGraphicsNotifyCallback Exit |

| 0x9A14 | SA | Initializing SA IPU device |

| 0x9A16 | SA | Initializing SA GNA device |

| 0x9A1A | SA | SaProgramLlcWays Start |

| 0x9A20 | SA | Initializing PciExpressInitPostMem |

| 0x9A22 | SA | Initializing ConfigureNorthIntelTraceHub |

| 0x9A30 | SA | Initializing Vtd |

| 0x9A31 | SA | Initializing TCSS |

| 0x9A32 | SA | Initializing Pavp |

| 0x9A34 | SA | PeiInstallSmmAccessPpi Start |

| 0x9A36 | SA | EdramWa Start |

| 0x9A4F | SA | Post-Mem SaInit Exit |

| 0x9A50 | SA | SaSecurityLock Start |

| 0x9A5F | SA | SaSecurityLock End |

| 0x9A60 | SA | SaSResetComplete Entry |

| 0x9A61 | SA | Set BIOS_RESET_CPL to indicate all configurations complete |

| 0x9A62 | SA | SaSvInit2 Start |

| 0x9A63 | SA | GraphicsPmInit Start |

| 0x9A64 | SA | SaPciPrint Start |

| 0x9A6F | SA | SaSResetComplete Exit |

| 0x9A70 | SA | SaS3ResumeAtEndOfPei Callback Entry |

| 0x9A7F | SA | SaS3ResumeAtEndOfPei Callback Exit |

| 0x9B00 | PCH | Post-Mem PchInit Entry |

| 0x9B03 | PCH | Post-Mem Tune the USB 2.0 high-speed signals quality |

| 0x9B04 | PCH | Post-Mem Tune the USB 3.0 signals quality |

| 0x9B05 | PCH | Post-Mem Configure PCH xHCI |

| 0x9B06 | PCH | Post-Mem Performs configuration of PCH xHCI SSIC |

| 0x9B07 | PCH | Post-Mem Configure PCH xHCI after init |

| 0x9B08 | PCH | Post-Mem Configures PCH USB device (xDCI) |

| 0x9B0A | PCH | Post-Mem DMI/OP-DMI configuration |

| 0x9B0B | PCH | Post-Mem Initialize P2SB controller |

| 0x9B0C | PCH | Post-Mem IOAPIC initialization |

| 0x9B0D | PCH | Post-Mem PCH devices interrupt configuration |

| 0x9B0E | PCH | Post-Mem HD Audio initizalization |

| 0x9B0F | PCH | Post-Mem HD Audio Codec enumeration |

| 0x9B10 | PCH | Post-Mem HD Audio Codec not detected |

| 0x9B13 | PCH | Post-Mem SCS initizalization |

| 0x9B14 | PCH | Post-Mem ISH initizalization |

| 0x9B15 | PCH | Post-Mem Configure SMBUS power management |

| 0x9B16 | PCH | Post-Mem Reserved |

| 0x9B17 | PCH | Post-Mem Performing global reset |

| 0x9B18 | PCH | Post-Mem Reserved |

| 0x9B19 | PCH | Post-Mem Reserved |

| 0x9B40 | PCH | Post-Mem OnEndOfPEI Entry |

| 0x9B41 | PCH | Post-Mem Initialize Thermal controller |

| 0x9B42 | PCH | Post-Mem Configure Memory Throttling |

| 0x9B47 | PCH | Post-Mem OnEndOfPEI Exit |

| 0x9B4D | PCH | Post-Mem Trace Hub - Memory configuration |

| 0x9B4E | PCH | Post-Mem Trace Hub - MSC0 configured |

| 0x9B4F | PCH | Post-Mem Trace Hub - MSC1 configured |

| 0x9B7F | PCH | Post-Mem PchInit Exit |

| 0x9C00 | CPU | CPU Post-Mem Entry |

| 0x9C09 | CPU | CpuAddConfigBlocks Done |

| 0x9C0A | CPU | SetCpuStrapAndEarlyPowerOnConfig Start |

| 0x9C13 | CPU | SetCpuStrapAndEarlyPowerOnConfig Reset |

| 0x9C14 | CPU | SetCpuStrapAndEarlyPowerOnConfig Done |

| 0x9C15 | CPU | CpuInit Start |

| 0x9C16 | CPU | SgxInitializationPrePatchLoad Start |

| 0x9C17 | CPU | CollectProcessorFeature Start |

| 0x9C18 | CPU | ProgramProcessorFeature Start |

| 0x9C19 | CPU | ProgramProcessorFeature Done |

| 0x9C20 | CPU | CpuInitPreResetCpl Start |

| 0x9C21 | CPU | ProcessorsPrefetcherInitialization Start |

| 0x9C22 | CPU | InitRatl Start |

| 0x9C23 | CPU | ConfigureSvidVrs Start |

| 0x9C24 | CPU | ConfigurePidSettings Start |

| 0x9C25 | CPU | SetBootFrequency Start |

| 0x9C26 | CPU | CpuOcInitPreMem Start |

| 0x9C27 | CPU | CpuOcInit Reset |

| 0x9C28 | CPU | BiosGuardInit Start |

| 0x9C29 | CPU | BiosGuardInit Reset |

| 0x9C3F | CPU | CpuInitPreResetCpl Done |

| 0x9C42 | CPU | SgxActivation Start |

| 0x9C43 | CPU | InitializeCpuDataHob Start |

| 0x9C44 | CPU | InitializeCpuDataHob Done |

| 0x9C4F | CPU | CpuInit Done |

| 0x9C50 | CPU | S3InitializeCpu Start |

| 0x9C55 | CPU | MpRendezvousProcedure Start |

| 0x9C56 | CPU | MpRendezvousProcedure Done |

| 0x9C69 | CPU | S3InitializeCpu Done |

| 0x9C6A | CPU | CpuPowerMgmtInit Start |

| 0x9C71 | CPU | InitPpm |

| 0x9C7F | CPU | CPU Post-Mem Exit |

| 0x9C80 | CPU | ReloadMicrocodePatch Start |

| 0x9C81 | CPU | ReloadMicrocodePatch Done |

| 0x9C82 | CPU | ApSafePostMicrocodePatchInit Start |

| 0x9C83 | CPU | ApSafePostMicrocodePatchInit Done |

1.8.10

1.8.10