|

CPU_CTRL_XMC1

|

Overview

The CPU_CTRL_XMC1 APP is a system APP. The CPU_CTRL_XMC1 APP provides functionality to configure the behavior of the CPU:

- Debug interface

- Exceptions

Debug Interface:

The XMC1 series implement various debug interfaces:

- SWD (Serial Wire Debug)

- SPD (Single Pin Debug)

The APP allows reserving the pins needed for the selected interface.

Following pins used for SWD: SWDCLK and SWDIO.

SWD0 (P0.14, P0.15), SWD1 (P1.3, P1.2)

Following pins used for SPD: SPDIO

SPD0(P0.14) and SPD1(P1.3)

Exceptions:

Exceptions in XMC1 series trap illegal memory access and illegal program behavior. The following types of faults are available:

- HardFault: A HardFault is an exception that occurs because of an error during exception processing, or because an exception cannot be managed by any other exception mechanism. HardFaults have a fixed priority of -1, meaning they have higher priority than any exception with configurable priority.

The APP allows generating code to make easier debugging the cause of hard fault.

Boot pin modes:

- Only available in XMC1400

- Reserves the P4.6 and P4.7 pins

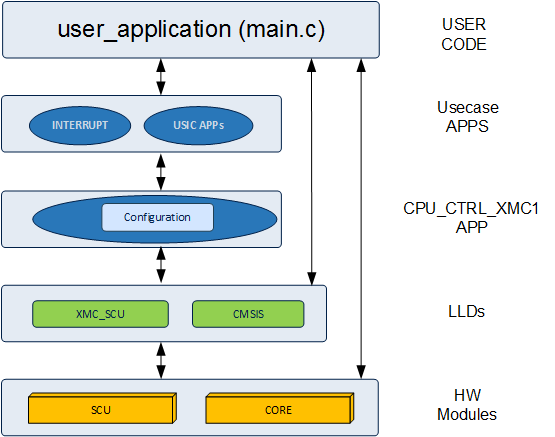

The figure below shows the APP structure in DAVE™. It uses the CMSIS library for configuring priority groups for interrupts used by the top level APPs.

Supported Devices

- XMC1400 Series

- XMC1300 Series

- XMC1200 Series

- XMC1100 Series

References

- XMC1400 Reference Manual

- XMC1300 Reference Manual

- XMC1200 Reference Manual

- XMC1100 Reference Manual