# **NI-DAQmx Device Considerations**

#### January 2008, 370738M-01

This help file contains information specific to analog output (AO) Series devices, C Series, B Series, E Series devices, digital I/O (DIO) devices, DSA devices, M Series devices, S Series devices, SCC devices, SCXI devices, switches, timing I/O (TIO) devices, and USB DAQ devices that might help you as you create applications with NI-DAQmx.

This document describes only NI-DAQmx. For information on Traditional NI-DAQ (Legacy), refer to the *Traditional NI-DAQ (Legacy) User Manual* or the *Traditional NI-DAQ (Legacy) Readme*.

© 2003–2008 National Instruments Corporation. All rights reserved.

# **Analog Triggering**

This section contains information about analog triggering for <u>C Series</u>, <u>DSA</u>, <u>E Series</u>, <u>M Series</u>, and <u>S Series</u> devices.

# Valid Analog Trigger Sources for DSA Devices

The analog trigger source must be a channel included in your physical channel list. PFI 0 is not a valid analog trigger source. PFI 0 is reserved for digital triggers.

### Analog Triggering Considerations for C Series, E Series, M Series, and S Series Devices

Note Not all E Series, M Series, S Series, and C Series devices support analog triggering. Refer to the specifications for your device to determine if your device supports analog triggering.

Many C Series, E Series, M Series, and S Series devices contain a single analog trigger circuit that you can configure for analog triggering. The analog trigger circuitry is a shared resource for the device, and any of the subsystems can use it. This trigger circuitry supports level and slope triggering with hysteresis as well as analog window triggering. After it is configured, the output of this circuitry appears as the Analog Comparison Event, which can be the source for various triggers and clocks within the analog input, analog output, and counter subsystems.

#### Sharing an Analog Trigger

Even though the analog trigger is a shared resource, only one analog input or analog output task at a time can configure and reserve it. If you want to share the analog trigger among multiple tasks, configure and reserve it in one task, and use the trigger in subsequent tasks by referring to the source of your trigger, clock, or signal of interest as the Analog Comparison Event. For tasks that support multiple types of analog triggers within the same task, all triggers must share the same configuration settings, or you receive an error. For instance, if you want to use an analog trigger for both your Start and Reference Trigger within an analog input task, the configuration settings for the start and Reference Trigger must be identical.

### E Series and S Series Valid Sources for the Analog Trigger PFI 0

Typically, when configuring an analog trigger, you connect your analog signal to the PFI 0 terminal. Because PFI 0 is the trigger source for both analog and digital signals, NI-DAQmx automatically tristates this terminal when a task exporting a signal on the terminal is not in the committed or running state. This behavior when exporting a signal on PFI 0 differs from typical task-based routing with other PFI lines. It prevents accidental connections of an analog signal directly to digital circuitry, which could permanently damage the device. Also, notice that when connecting an analog signal to PFI 0, the terminal configuration is referenced single-ended.

Even when PFI 0 is not the source of your analog trigger, you cannot use PFI 0 for other digital signal routes because the analog trigger takes over the PFI 0 terminal internal to the device when it is enabled. If you try to use the analog trigger and PFI 0 for digital signals at the same time, you receive a routing error.

Note On NI PXI-6132/6133 devices, you cannot use PFI 0 as the source of an analog trigger, but the analog triggering circuitry still reserves PFI 0 for internal routing.

#### **Analog Input Channel**

In addition to PFI 0, analog input tasks can trigger off of one of the analog input channels being sampled. Because E Series devices use a scanning architecture, many restrictions are placed on how you can use an analog trigger when the source is one of the channels you are sampling. When you use an analog Start Trigger, the trigger channel must be the first channel in the channel list. When you use an Analog Reference or Pause Trigger, and the analog channel is the source of the trigger, there can be only one channel in the channel list. If you have more than one channel for Pause or Reference Triggers, you must use PFI 0. Since S Series devices do not use a scanning architecture, none of these restrictions apply. Therefore, for an S Series device, you can use any analog input channel as the source of the trigger regardless of how many channels are being sampled or the order of the trigger channel in the sequence.

#### Scaling with PFI 0 and Analog Input Channels

Scaling, including custom scales, is not applied if PFI 0 is the trigger source. For instance, you would specify the DAQmx Trigger **analog edge level** attribute/property in volts. However, if you use an analog input channel as the trigger source, you could use scaled units.

### M Series Valid Sources for the Analog Trigger

#### APFI 0 and APFI 1

When configuring an analog trigger, connect your analog signal to either the APFI 0 or APFI 1 terminal and specify APFI 0 or APFI 1 as your trigger source.

#### **Analog Input Channel**

In addition to APFI 0 and APFI 1, analog input tasks can trigger off of one of the analog input channels being sampled. Because M Series devices use a scanning architecture, many restrictions are placed on how you can use an analog trigger when the source is one of the channels you are sampling. When you use an Analog Start Trigger, the trigger channel must be the first channel in the channel list. When you use an Analog Reference or Pause Trigger, and the analog channel is the source of the trigger, there can be only one channel in the channel list. If you have more than one channel for Pause or Reference Triggers, you must use APFI 0 or APFI 1.

#### Scaling with APFI 0, APFI 1, and Analog Input Channels

Scaling, including custom scales, is not applied if APFI 0 or APFI 1 is the trigger source. For instance, you would specify the DAQmx Trigger **analog edge level** attribute/property in volts. However, if you use an analog input channel as the trigger source, you could use scaled units.

#### **Device Calibration and Accuracy of the Analog Trigger**

The trigger DACs in the analog trigger circuitry on an E Series, M Series, C Series, or S Series device typically contain four less bits of accuracy than the ADC of the device. No hardware calibration is provided for the analog trigger circuitry. In addition, the propagation delay from when a valid trigger condition is met to when the analog trigger circuitry emits the Analog Comparison Event may have an impact on your measurements if the trigger signal has a high slew rate. If you find these conditions have a noticeable impact on your measurements, you can perform software calibration on the analog trigger circuitry by configuring your task as normal and applying a known signal for your analog trigger. Comparing the observed results against the expected results, you can calculate the necessary offsets to apply in software to fine tune the desired triggering behavior.

### C Series Valid Sources for the Analog Trigger

#### **Analog Input Channel**

The NI 9205 has no APFI 0 or APFI 1 terminal. Analog input tasks using the NI 9205 can trigger off one of the analog input channels being sampled by the NI 9205. When you use an Analog Start Trigger, the trigger channel must be the first channel from the NI 9205 in the channel list, but channels from other C Series devices can come first. When you use an Analog Reference or Pause Trigger, you can use only one channel from the NI 9205 in the channel list, but you can use channels from other C Series devices. You can combine Analog Start, Reference, and Pause Triggers with different configuration settings by using multiple NI 9205 devices. All analog triggers on the same device must share the same configuration settings.

# **Device Calibration Considerations**

*Device calibration* consists of verifying the measurement accuracy of a device and adjusting for any measurement error. Verification consists of measuring the performance of the device and comparing these measurements to the published specifications. During calibration, you supply and read voltage levels or other signals using external standards, then you adjust the device calibration constants. The new calibration constants are stored in the EEPROM. These calibration constants are loaded from memory as needed to adjust for the error in the measurements taken by the device.

This section contains information needed for device calibration:

- AO Series

- <u>DSA</u>

- <u>E Series</u>

- <u>M Series, NI 6010, NI 9205, NI 9206</u>

- <u>NI 6154</u>

- <u>NI PXI-6608</u>

- <u>S Series</u>

- <u>SCXI-1600</u>

# **AO Series Calibration**

Your device uses software calibration to fine-tune the analog output circuitry. The software must be programmed (or loaded) with certain numbers called calibration constants. Those constants are stored in nonvolatile memory (EEPROM) on your device or are maintained by NI-DAQmx. To achieve specification accuracy, you should self-calibrate your device just before a measurement session but after your computer and the device have been powered on and warmed up for at least 15 minutes. You should allow this same warm-up time before performing any calibration of your system. Frequent calibration produces the most stable and repeatable measurement performance. The device is not harmed in any way if you recalibrate it often.

Static AO devices, such as the NI 6703 and NI 6704, do not self-calibrate or automatically calibrate. You must use a manual procedure to calibrate static AO devices.

Refer to <u>ni.com/calibration</u> for detailed instructions about calibrating your device.

Note Calibrating your AO device takes some time. Do not be alarmed if the Self-Calibrate or Adjust AO Series Calibration function/VI takes several seconds to execute.

**Note** For best results, stop any ongoing tasks and disconnect any unnecessary external connections before running calibration.

### **Calibration Constant Loading by NI-DAQmx**

NI-DAQmx automatically loads calibration constants into the software whenever you call functions/VIs that depend on them.

#### **Related Topic**

Calibration Signal Connections for AO Series Devices

# **Virtual Channel Calibration Support**

The following devices do not support NI-DAQmx virtual channel calibration:

- NI DAQPad-6015

- NI DAQPad-6016

- NI PCI-6010

- NI PCI-6013

- NI PCI-6014

- NI USB-6008

- NI USB-6009

- SensorDAQ

# **DSA Calibration**

Your device contains digital correction circuitry to compensate for gain and offset errors in the analog and ADC circuitry. The gain and offset calibration constants are stored in nonvolatile memory (EEPROM) on your device. NI-DAQmx writes these calibration constants to the digital correction circuitry.

To achieve the maximum accuracy, you should perform external calibration at least once per year (the recommended external calibration interval) and perform self-calibration prior to measurement sessions or otherwise, as desired. You should calibrate your device only after your computer and the device have been powered on and warmed up for at least 15 minutes.

#### **Self-Calibration**

Self-calibration is executed with the Self Calibrate VI/function. When you self-calibrate a DSA device, you do not need signal connections. However, for devices with analog output channels, values generated on those output channels can change during the calibration process. If you have external equipment connected to the AO channels and changing the AO voltage could damage the external equipment, you should disconnect the external equipment before performing the self-calibration.

### **External Calibration**

External calibration is performed using a customized calibration program and external test equipment that has itself been calibrated to the required accuracy or standard. This operation is usually performed by a specialized metrology laboratory. The equipment and connections required to externally calibrate a device varies depending on the device category. For NI PXI-447*X* and PXI-446*X* devices, you need a stable and accurate DC voltage signal to calibrate the AI subsystem. NI PXI-446*X* devices also include an adjustable frequency timebase. You need a stable sinusoidal frequency source to calibrate this timebase. The NI PXI-4461 also supports analog output. You need a digital multimeter (DMM) to calibrate the AO subsystem. The DC voltage, frequency source, and DMM can be manually or automatically controlled and switched between channels, depending on the nature of the customized calibration program.

# **E** Series Calibration

Your device uses hardware calibration to adjust the analog circuitry. This calibration is done with calibration digital-to-analog converters, called calDACs, that fine-tune the analog circuitry. The calDACs must be programmed (or loaded) with certain numbers called calibration constants. Those constants are stored in nonvolatile memory (EEPROM) on your device or are maintained by NI-DAQmx. NI recommends that you self-calibrate your device just before a measurement session but after your computer and the device have been powered on and warmed up for at least 15 minutes. You should allow this same warm-up time before performing any calibration of your system. Frequent calibration produces the most stable and repeatable measurement performance. The device is not harmed in any way if you recalibrate it often.

$\overline{\mathbb{N}}$

**Note** Calibrating your MIO or AI device takes some time. Do not be alarmed if the Self-Calibrate or Adjust E Series Calibration function/VI takes several seconds to execute.

Note For best results, stop any ongoing tasks and disconnect any unnecessary external connections before running calibration.

### **Calibration Constant Loading by NI-DAQmx**

NI-DAQmx automatically loads calibration constants into calDACs whenever you call functions/VIs that depend on them. The following conditions apply:

- 12-bit E Series devices

- 12-bit devices use a single set of calibration constants for both unipolar and bipolar modes of analog input.

- One set of constants is valid for unipolar, and another set is valid for bipolar configuration of the analog output channels. When you change the polarity of an analog output channel, NI-DAQmx reloads the calibration constants for that channel.

- 16-bit E Series devices

- Calibration constants required by the 16-bit E Series devices for unipolar analog input channels are different from those for bipolar analog input channels. If you are acquiring data from one channel, or if all of the channels you are acquiring data from are configured for the same polarity, NI-DAQmx selects the appropriate set of calibration constants for you. If you are scanning several channels, and you mix channels configured for unipolar and bipolar mode in your scan list, NI-DAQmx loads the calibration constants that correspond to the first channel in the scan list.

- NI 6025E devices use a single set of calibration constants for both unipolar and bipolar modes of analog input.

- One set of constants is valid for unipolar, and another set is valid for bipolar configuration of the analog output channels. When you change the polarity of an analog output channel, NI-DAQmx reloads the calibration constants for that channel.

#### **Related Topic**

Calibration Signal Connections for E Series Devices

# M Series, NI 6010, NI 9205, and NI 9206 Calibration

Your device uses software calibration to adjust the software scaling of signals read from and produced by your device. Using calibration pulse width modulated (PWM) sources with a reference voltage, your device measures and calculates scaling constants for analog input and analog output. The scaling constants are stored in nonvolatile memory (EEPROM) on your device. NI recommends that you self-calibrate your device just before a measurement session but after your computer and the device have been powered on and warmed up for at least 15 minutes. You should allow this same warm-up time before performing any calibration of your system. Frequent calibration produces the most stable and repeatable measurement performance. The device is not harmed in any way if you recalibrate it often.

$\overline{\mathbb{N}}$

**Note** Calibrating your device takes some time. Do not be alarmed if the Self-Calibrate or Adjust M Series Calibration function/VI takes several seconds to execute.

Note For best results, stop any ongoing tasks and disconnect any unnecessary external connections before running calibration.

# NI 6154 Calibration

Your device uses software calibration to adjust the software scaling of signals read from and produced by your device. Using calibration pulse-width modulated (PWM) sources with a reference voltage, your device measures and calculates scaling constants for analog input and analog output. The scaling constants are stored in nonvolatile memory (EEPROM) on your device. NI recommends that you self-calibrate your device just before a measurement session but after your computer and the device have been powered on and warmed up for at least 15 minutes. You should allow this same warm-up time before performing any calibration of your system. Frequent calibration produces the most stable and repeatable measurement performance. The device is not harmed in any way if you recalibrate it often.

**Note** Calibrating your device takes some time. Do not be alarmed if the Self-Calibrate or Adjust S Series Calibration function/VI takes several seconds to execute.

Note For best results, stop any ongoing tasks and disconnect any unnecessary external connections before running calibration.

# **NI PXI-6608 Calibration**

You cannot calibrate the PXI-6608 in NI-DAQmx. The device must be calibrated in Traditional NI-DAQ (Legacy). To use the NI PXI-6608 in NI-DAQmx after calibrating it in Traditional NI-DAQ (Legacy), you must do one of the following:

• Call the Traditional NI-DAQ (Legacy) Device Reset function/VI.

—or—

• Right-click the **Traditional NI-DAQ (Legacy) Devices** folder in MAX and select **Reset Driver for Traditional NI-DAQ**.

# **S** Series Calibration

Your device uses hardware calibration to adjust the analog circuitry. This calibration is done with calibration digital-to-analog converters, called calDACs, that fine-tune the analog circuitry. The calDACs must be programmed (or loaded) with certain numbers called calibration constants. Those constants are stored in nonvolatile memory (EEPROM) on your device or are maintained by NI-DAQmx. NI recommends that you self-calibrate your device just before a measurement session but after your computer and the device have been powered on and warmed up for at least 15 minutes. You should allow this same warm-up time before performing any calibration of your system. Frequent calibration produces the most stable and repeatable measurement performance. The device is not harmed in any way if you recalibrate it often.

$\overline{\mathbb{N}}$

**Note** Calibrating your MIO or AI device takes some time. Do not be alarmed if the DAQmx Self-Calibrate or Adjust S Series Calibration function/VI takes several seconds to execute.

Note For best results, stop any ongoing tasks and disconnect any unnecessary external connections before running calibration.

### **Calibration Constant Loading by NI-DAQmx**

NI-DAQmx automatically loads calibration constants into the calDACs whenever you call functions/VIs that depend on them. The following conditions apply:

- One set of calibration constants is required for each analog input channel on an S Series device. Within this set of calibration channels, different calibration constants are stored for each analog input range supported by the S Series device. When you configure an acquisition, NI-DAQmx automatically loads the calibration constants for each channel, based on its configured input range.

- One set of calibration constants is required for each analog output channel. When an you configure analog output generation, NI-DAQmx automatically loads the calDACs for each channel configured.

#### **Related Topic**

Calibration Signal Connections for S Series Devices

# **SCXI-1600** Calibration

The external calibration process for the SCXI-1600 module is nearly identical to the E Series devices. However, when applying a precision voltage to the module, you must connect the signal to the EXTCAL BNC connector on the front of the SCXI-1600, instead of the AI0 analog input channel. In LabVIEW, use the Adjust E-Series Calibration VI, instead of the Adjust SC Baseboard Calibration VI.

# **Signal Connections**

This section contains information about calibration signal connections for <u>AO Series</u>, <u>E Series</u>, <u>M Series</u>, <u>NI 6010</u>, <u>NI 6154</u>, and <u>S Series</u> devices.

# Device Calibration Signal Connections for AO Series Devices

#### **Self-Calibration**

When you self-calibrate your AO Series device, no signal connections are necessary. However, values generated on the analog output channels change during the calibration process.

### **External Calibration**

When externally calibrating your AO Series device, connect the signals as described below for the type of AO Series device you are calibrating. Set the reference voltage between +6.000 V and +9.999 V. Typically, you use a calibrator or other stable voltage source for the reference voltage. Do not use a power supply as its signals are not very stable.

Follow these steps for AO Series devices:

- 1. Connect the positive output of your reference voltage source to the EXT REF terminal.

- 2. Connect the negative output of your reference voltage source to the AO GND terminal.

For more information about calibration procedures for static AO devices, refer to the device documentation or to <u>Calibration Procedures</u>.

# Device Calibration Signal Connections for E Series Devices

#### **Self-Calibration**

When you self-calibrate your E Series device, no signal connections are necessary. However, values generated on the analog output channels change during the calibration process. If you have external circuitry connected to the analog output channels and you do not want changes on these channels, you should disconnect the circuitry before beginning the self-calibration.

### **External Calibration**

When externally calibrating your E Series device, connect the signals as described below for the type of E Series device you are calibrating. Set the reference voltage between +6.000 V and +9.999 V. Typically, you use a calibrator or other stable voltage source for the reference voltage. Do not use a power supply as its signals are not very stable.

#### **12-Bit E Series Devices**

Follow these steps for 12-bit E Series devices:

- 1. Connect the positive output of your reference voltage source to physical channel ai8.

- 2. Connect the negative output of your reference voltage source to the AI SENSE terminal.

- 3. Connect physical channel ao0 to physical channel ai0.

- 4. If your reference voltage source and your computer are floating with respect to each other, connect the AI SENSE terminal to the AI GND terminal as well as to the negative output of your reference voltage source.

#### **16-Bit E Series Devices**

Follow these steps for 16-bit E Series devices:

- 1. Connect the positive output of your reference voltage source to physical channel ai0.

- 2. Connect the negative output of your reference voltage source to physical channel ai8.

- 3. If your reference voltage source and your computer are floating with respect to each other, connect the negative output of your reference voltage source to the AI GND terminal as well as to physical channel ai8.

# How Does Calibration in NI-DAQmx Differ from Calibration in Traditional NI-DAQ (Legacy)?

In Traditional NI-DAQ (Legacy), several 16-bit devices use the 12-bit signal connection scheme (the NI PCI-6034, NI PCI-6035, NI 6036 and NI PCI/PXI 6052). In NI-DAQmx, all of these devices now use the 16-bit E Series connections.

# Device Calibration Signal Connections for S Series Devices

#### **Self-Calibration**

When you self-calibrate your S Series device, no signal connections are necessary. However, values generated on the analog output channels change during the calibration process. If you have external circuitry connected to the analog output channels that is sensitive to these changes, you should disconnect the circuitry before beginning selfcalibration.

### **External Calibration**

When externally calibrating your S Series device, connect the signals as described below. Set the reference voltage to the following:

- NI PCI/PXI 6143: between 3.0 V and 4.998 V

- NI PCI/PXI 6115: between 4.995 V and 5.005 V

- NI PCI/PXI 6120: between 4.995 V and 5.005 V

- All other S Series Devices: between 6.0 V and 9.998 V

Typically, you should use a calibrator or other stable voltage source for calibration. Do not use a power supply as its signals are not very stable. For external calibration, make the following signal connections:

- 1. Connect the positive output of your reference voltage source to ACH0+.

- 2. Connect the negative output of your reference voltage source to ACH0-.

# Device Calibration Signal Connections for M Series and NI 6010 Devices

#### **Self-Calibration**

When you self-calibrate your M Series or NI 6010 device, no signal connections are necessary. However, values generated on the analog output channels change during the calibration process. If you have external circuitry connected to the analog output channels and you do not want changes on these channels, you should disconnect the circuitry before beginning the self-calibration.

### **External Calibration**

When externally calibrating your M Series or NI 6010 device, connect the signals as described below for the type of device you are calibrating. Set the reference voltage between +6.0 V and +8.5 V for M Series devices, between +3.5 V and 4.0 V for NI 6010 devices. Typically, you use a calibrator or other stable voltage source for the reference voltage. Do not use a power supply as its signals are not very stable.

Follow these steps:

- 1. Disconnect any external connections or circuitry to your device.

- 2. Connect the positive output of your reference voltage source to physical channel ai0.

- 3. Connect the negative output of your reference voltage source to physical channel ai8.

- 4. If your reference voltage source and your computer are floating with respect to each other, connect the negative output of your reference voltage source to the AI GND terminal as well as to physical channel ai8.

# **Device Calibration Signal Connections for the NI** 6154

### **Self-Calibration**

When you self-calibrate your NI 6154 device, no signal connections are necessary. However, values generated on the analog output channels change during the calibration process.

#### **External Calibration**

When externally calibrating your NI 6154 device, connect the signals as described below for the type of device you are calibrating. Set the reference voltage between +6.0 V and +9.998 V. Typically, you use a calibrator or other stable voltage source for the reference voltage. Do not use a power supply as its signals are not very stable.

Follow these steps:

- 1. Disconnect any external connections or circuitry to your device.

- 2. Connect the positive output of your reference voltage source to physical channel AI0+.

- 3. Connect the negative output of your reference voltage source to physical channel AIO-.

## Counters

This section contains information on <u>counter signal connections</u> and block diagrams that illustrate the <u>internal counter routing</u>.

## **Connecting Counter Signals**

The default terminals used for counter measurements and generations vary from device to device. Follow the links below for information specific to your device. To override the default input terminal, set the DAQmx Channel **Input Terminal** attribute/property for the measurement type. For instance, if you are counting edges, you would use **Counter Input:Count Edges:Input Terminal**. To override the default output terminal, set the DAQmx Channel **Output Terminal** attribute/property to the desired value.

#### **Related Topics**

AO Series, E Series, and S Series Signal Connections for Counters Bus-Powered M Series Signal Connections for Counters C Series Signal Connections for Counters M Series Signal Connections for Counters 37-Pin DSUB Signal Connections for Counters TIO Signal Connections for Counters

# **Bus-Powered M Series Signal Connections for Counters**

The following table lists the default input terminals for various counter measurements on <u>bus-powered M Series devices</u>. You can use a different PFI line for any of the input terminals. To change the PFI input for a measurement, use the NI-DAQmx channel attributes/properties.

| Measurement                                                        | Ctr0                                         | Ctr1                                          |

|--------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|

| Count Edges                                                        | Edges: PFI 0<br>Count<br>Direction:<br>PFI 9 | Edges: PFI 3<br>Count<br>Direction: PFI<br>10 |

| Pulse Width Measurement                                            | PFI 1                                        | PFI 2                                         |

| Period/Frequency Measurement (Low Frequency with One Counter)      | PFI 1                                        | PFI 2                                         |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 0                                        | PFI 3                                         |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 0                                        | PFI 3                                         |

| Semiperiod Measurement                                             | PFI 1                                        | PFI 2                                         |

| Two-Edge Separation Measurement                                    | Start: PFI 9<br>Stop: PFI 1                  | Start: PFI 10<br>Stop: PFI 2                  |

| Position Measurement                                               | A: PFI 0<br>B: PFI 9<br>Z: PFI 1             | A: PFI 3<br>B: PFI 10<br>Z: PFI 2             |

#### 16-PFI Line Devices (NI 6218)

#### 16-PFI Line Devices (NI 6212/6216)

| Measurement             | Ctr0                                          | Ctr1  |

|-------------------------|-----------------------------------------------|-------|

| Count Edges             | Edges: PFI 8<br>Count<br>Direction: PFI<br>10 | Count |

| Pulse Width Measurement | PFI 9                                         | PFI 4 |

| Period/Frequency Measurement (Low<br>Frequency with One Counter)   | PFI 9                             | PFI 4                             |

|--------------------------------------------------------------------|-----------------------------------|-----------------------------------|

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 8                             | PFI 3                             |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 8                             | PFI 3                             |

| Semiperiod Measurement                                             | PFI 9                             | PFI 4                             |

| Two-Edge Separation Measurement                                    | Start: PFI 10<br>Stop: PFI 9      | Start: PFI 11<br>Stop: PFI 4      |

| Position Measurement                                               | A: PFI 8<br>B: PFI 10<br>Z: PFI 9 | A: PFI 3<br>B: PFI 11<br>Z: PFI 4 |

The following table lists the output terminals for counter output. You can use a different PFI line for any of the output terminals.

| Ctr0   | Ctr1   |

|--------|--------|

| PFI 12 | PFI 13 |

#### 8-PFI Line Devices (Such as the NI 6210/6211/6215)

| Measurement                                                        | Ctr0                                         | Ctr1                                         |

|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Count Edges                                                        | Edges: PFI 0<br>Count<br>Direction:<br>PFI 0 | Edges: PFI 3<br>Count<br>Direction: PFI<br>3 |

| Pulse Width Measurement                                            | PFI 1                                        | PFI 2                                        |

| Period/Frequency Measurement (Low<br>Frequency with One Counter)   | PFI 1                                        | PFI 2                                        |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 0                                        | PFI 3                                        |

| Period/Frequency Measurement (Large<br>Range with Two Counters)    | PFI 0                                        | PFI 3                                        |

| Semiperiod Measurement                                             | PFI 1                                        | PFI 2                                        |

| Two-Edge Separation Measurement                                    | Start: PFI 0<br>Stop: PFI 1                  | Start: PFI 3<br>Stop: PFI 2                  |

|                                                                    |                                              |                                              |

| Position Measurement | A: PFI 0 | A: PFI 3 |

|----------------------|----------|----------|

|                      | B: PFI 1 | B: PFI 2 |

|                      | Z: PFI 2 | Z: PFI 1 |

The following table lists the output terminals for counter output. You can use a different PFI line for any of the output terminals.

## **C** Series Signal Connections for Counters

The following table lists the default input terminals for various counter measurements. You can use a different PFI line for any of the input terminals. To change the PFI input for a measurement, use the NI-DAQmx channel attributes/properties.

| Measurement                                                        | Ctr0                                         | Ctr1                                         |

|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Count Edges                                                        | Edges: PFI 0<br>Count<br>Direction:<br>PFI 2 | Edges: PFI 4<br>Count<br>Direction: PFI<br>6 |

| Pulse Width Measurement                                            | PFI 1                                        | PFI 5                                        |

| Period/Frequency Measurement (Low Frequency with One Counter)      | PFI 1                                        | PFI 5                                        |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 0                                        | PFI 4                                        |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 0                                        | PFI 4                                        |

| Semiperiod Measurement                                             | PFI 1                                        | PFI 5                                        |

| Two-Edge Separation Measurement                                    | Start: PFI 2<br>Stop: PFI 1                  | Start: PFI 6<br>Stop: PFI 5                  |

| Position Measurement                                               | A: PFI 0<br>B: PFI 2<br>Z: PFI 1             | A: PFI 4<br>B: PFI 6<br>Z: PFI 5             |

#### NI 9401, NI 9421, NI 9422, and NI 9423

#### NI 9402

| Measurement                                                        | Ctr0                                         | Ctr1                                         |

|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Count Edges                                                        | Edges: PFI 0<br>Count<br>Direction:<br>PFI 2 | Edges: PFI 3<br>Count<br>Direction: PFI<br>1 |

| Pulse Width Measurement                                            | PFI 1                                        | PFI 2                                        |

| Period/Frequency Measurement (Low<br>Frequency with One Counter)   | PFI 1                                        | PFI 2                                        |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 0                                        | PFI 3                                        |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 0                                        | PFI 3                                        |

| Semiperiod Measurement                                             | PFI 1                                        | PFI 2                                        |

| Two-Edge Separation Measurement                                    | Start: PFI 2<br>Stop: PFI 1                  | Start: PFI 1<br>Stop: PFI 2                  |

| Position Measurement                                               | A: PFI 0<br>B: PFI 2<br>Z: PFI 1             | A: PFI 3<br>B: PFI 1<br>Z: PFI 2             |

#### NI 9411

| Measurement                                                        | Ctr0                                         | Ctr1                                         |

|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Count Edges                                                        | Edges: PFI 0<br>Count<br>Direction:<br>PFI 2 | Edges: PFI 3<br>Count<br>Direction: PFI<br>5 |

| Pulse Width Measurement                                            | PFI 1                                        | PFI 4                                        |

| Period/Frequency Measurement (Low<br>Frequency with One Counter)   | PFI 1                                        | PFI 4                                        |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 0                                        | PFI 3                                        |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 0                                        | PFI 3                                        |

| Semiperiod Measurement                                             | PFI 1                                        | PFI 4                                        |

| Two-Edge Separation Measurement                                    | Start: PFI 2<br>Stop: PFI 1                  | Start: PFI 5<br>Stop: PFI 4                  |

| Position Measurement                                               | A: PFI 0<br>B: PFI 2<br>Z: PFI 1             | A: PFI 3<br>B: PFI 5<br>Z: PFI 4             |

The following tables list the output terminals for counter output. You can use a different PFI line for any of the output terminals.

#### NI 9401, NI 9472, NI 9474, and NI 9485

| Ctr0  | Ctr1  |

|-------|-------|

| PFI 3 | PFI 7 |

NI 9481 and NI 9402

### AO Series, E Series, and S Series Signal Connections for Counters

The following table lists the default input terminals for various counter measurements. You can use a different PFI line for any of the input terminals, with the exception of the count direction terminal for edge counting. To change the PFI input for a measurement, use the NI-DAQmx channel attributes/properties.

| Measurement                                                                            | Ctr0                                             | Ctr1                                             |

|----------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Count Edges                                                                            | Edges: PFI 8                                     | Edges: PFI 3                                     |

|                                                                                        | Count<br>Direction <sup>1</sup> :<br>port0/line6 | Count<br>Direction <sup>1</sup> :<br>port0/line7 |

| Pulse Width Measurement                                                                | PFI 9                                            | PFI 4                                            |

| Period/Frequency Measurement (Low Frequency with One Counter)                          | PFI 9                                            | PFI 4                                            |

| Period/Frequency Measurement (High<br>Frequency with Two Counters)                     | PFI 8                                            | PFI 3                                            |

| Period/Frequency Measurement<br>(Large Range with Two Counters)                        | PFI 8                                            | PFI 3                                            |

| Semiperiod Measurement                                                                 | PFI 9                                            | PFI 4                                            |

| <sup>1</sup> The count direction terminal must be tristated to use an external signal. |                                                  |                                                  |

Reset the device to ensure the terminal is tristated.

The following table lists the default output terminals for counter output. You must use the default output terminal, with the exception that for Ctr0, you can select a RTSI line.

| Ctr0      | Ctr1      |

|-----------|-----------|

| CTR 0 OUT | CTR 1 OUT |

## **TIO Signal Connections for Counters**

The following table lists the default input terminals for various counter measurements. You can use a different PFI line for any of the input terminals. To change the PFI input for a measurement, use the NI-DAQmx channel properties/attributes.

| Measurement                                                                 | Ctr0                          | Ctr1                          | Ctr2                          | Ctr3                          | Ctr4                          |                |

|-----------------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|----------------|

| Count Edges                                                                 | Edges:<br>PFI 39              | Edges:<br>PFI 35              | Edges:<br>PFI 31              | Edges:<br>PFI 27              | Edges:<br>PFI 23              | Ec<br>PF       |

|                                                                             | Count<br>Direction:<br>PFI 37 | Count<br>Direction:<br>PFI 33 | Count<br>Direction:<br>PFI 29 | Count<br>Direction:<br>PFI 25 | Count<br>Direction:<br>PFI 21 | Cc<br>Di<br>PF |

| Pulse Width<br>Measurement                                                  | PFI 38                        | PFI 34                        | PFI 30                        | PFI 26                        | PFI 22                        | PF             |

| Period/Frequency<br>Measurement<br>(Low Frequency<br>with One<br>Counter)   | PFI 38                        | PFI 34                        | PFI 30                        | PFI 26                        | PFI 22                        | PF             |

| Period/Frequency<br>Measurement<br>(High Frequency<br>with Two<br>Counters) | PFI 39                        | PFI 35                        | PFI 31                        | PFI 27                        | PFI 23                        | PF             |

| Period/Frequency<br>Measurement<br>(Large Range<br>with Two<br>Counters)    | PFI 39                        | PFI 35                        | PFI 31                        | PFI 27                        | PFI 23                        | PF             |

| Semiperiod<br>Measurement                                                   | PFI 38                        | PFI 34                        | PFI 30                        | PFI 26                        | PFI 22                        | PF             |

| Two-Edge<br>Separation<br>Measurement                                       | Start:<br>PFI 37              | Start:<br>PFI 33              | Start:<br>PFI 29              | Start:<br>PFI 25              | Start:<br>PFI 21              | Sti<br>PF      |

|                              | Stop:<br>PFI 38 | Stop:<br>PFI 34 | Stop:<br>PFI 30 | Stop:<br>PFI 26 | Stop:<br>PFI 22 | St<br>PF |

|------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|

| Position<br>Measurement      | A: PFI 39       | A: PFI 35       | A: PFI 31       | A: PFI 27       | A: PFI 23       | A:       |

|                              | B: PFI 37       | B: PFI 33       | B: PFI 29       | B: PFI 25       | B: PFI 21       | B:       |

|                              | Z: PFI 38       | Z: PFI 34       | Z: PFI 30       | Z: PFI 26       | Z: PFI 22       | Z:       |

| GPS Timestamp<br>Measurement | N/A             | N/A             | N/A             | N/A             | N/A             | N/       |

Note The NI 6601 has only four counters (ctr0–ctr3). The entries in the previous table for cntr4, cntr5, cntr6, and cntr7 do not apply for that device.

The following table lists the output terminals for counter output. You can use a different PFI line for any of the output terminals.

| Ctr0   | Ctr1   | Ctr2   | Ctr3   | Ctr4   | Ctr5   | Ctr6   | Ctr7  |

|--------|--------|--------|--------|--------|--------|--------|-------|

| PFI 36 | PFI 32 | PFI 28 | PFI 24 | PFI 20 | PFI 16 | PFI 12 | PFI 8 |

**Note** The NI 6601 has only four counters (ctr0–ctr3). The entries in the previous table for cntr4, cntr5, cntr6, and cntr7 do not apply for that device.

#### NI 6624 Issues

The eight PFI lines listed as the defaults for counter output are dedicated for output, and they are the only terminals you can use for counter output. For example, you can use PFI 8 (the default for Ctr7) as the output terminal for any counter, but you cannot use it as an input terminal.

When using counter output, if the **Idle State** attribute/property is low, the optocouplers on the NI 6624 will still be driving your output load. Set the **Idle State** attribute/property to high to prevent driving the output after your task completes.

## **37-Pin DSUB Signal Connections for Counters**

The following table lists the default input terminals for various counter measurements for devices that use the 37-Pin DSUB connector such as the NI 6010, NI 6154, and NI 623*X*. You can use a different PFI line for any of the input terminals. To change the PFI input for a measurement, use the NI-DAQmx channel attributes/properties.

#### Input

| Measurement                                                        | Ctr0                                         | Ctr1                                         |

|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Count Edges                                                        | Edges: PFI 0<br>Count<br>Direction:<br>PFI 2 | Edges: PFI 3<br>Count<br>Direction: PFI<br>5 |

| Pulse Width Measurement                                            | PFI 1                                        | PFI 4                                        |

| Period/Frequency Measurement (Low<br>Frequency with One Counter)   | PFI 1                                        | PFI 4                                        |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 0                                        | PFI 3                                        |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 0                                        | PFI 3                                        |

| Semiperiod Measurement                                             | PFI 1                                        | PFI 4                                        |

The following table lists the output terminals for counter output. You can use a different PFI line for any of the output terminals.

| Output |

|--------|

|--------|

## 68-Pin M Series Signal Connections for Counters

The following table lists the default input terminals for various counter measurements on M Series devices, including M Series USB devices, such as the NI USB 6259 screw terminal and NI USB-6229 BNC devices. You can use a different PFI line for any of the input terminals. To change the PFI input for a measurement, use the NI-DAQmx channel attributes/properties.

| Measurement                                                        | Ctr0                                          | Ctr1                                          |

|--------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| Count Edges                                                        | Edges: PFI 8<br>Count<br>Direction: PFI<br>10 | Edges: PFI 3<br>Count<br>Direction: PFI<br>11 |

| Pulse Width Measurement                                            | PFI 9                                         | PFI 4                                         |

| Period/Frequency Measurement (Low<br>Frequency with One Counter)   | PFI 9                                         | PFI 4                                         |

| Period/Frequency Measurement (High<br>Frequency with Two Counters) | PFI 8                                         | PFI 3                                         |

| Period/Frequency Measurement (Large Range with Two Counters)       | PFI 8                                         | PFI 3                                         |

| Semiperiod Measurement                                             | PFI 9                                         | PFI 4                                         |

| Two-Edge Separation Measurement                                    | Start: PFI 10<br>Stop: PFI 9                  | Start: PFI 11<br>Stop: PFI 4                  |

| Position Measurement                                               | A: PFI 8<br>B: PFI 10<br>Z: PFI 9             | A: PFI 3<br>B: PFI 11<br>Z: PFI 4             |

The following table lists the output terminals for counter output. You can use a different PFI line for any of the output terminals.

| Ctr0   | Ctr1   |  |

|--------|--------|--|

| PFI 12 | PFI 13 |  |

Note Some M Series devices, including the NI 6010, NI 6154, NI 6221 (37-pin), and NI 623X, use the 37-pin DSUB connector. These devices have different counter terminal defaults. Refer to the <u>37-Pin DSUB Signal Connections for Counters</u> for the default input terminals on these devices. Bus-powered M Series devices, such as the NI USB-621*X* devices, also have different counter terminal defaults. Refer to the <u>Bus-Powered M Series Signal</u> <u>Connections for Counters</u> for the default input terminals on these devices.

## **Counter Internal Routing Diagrams**

This section contains block diagrams that illustrate the internal counter routing for <u>AO Series</u>, <u>C Series</u>, <u>E Series</u>, <u>M Series</u>, <u>S Series</u>, and <u>TIO</u> devices.

### AO Series, E Series, S Series Counter Internal Routing Diagram

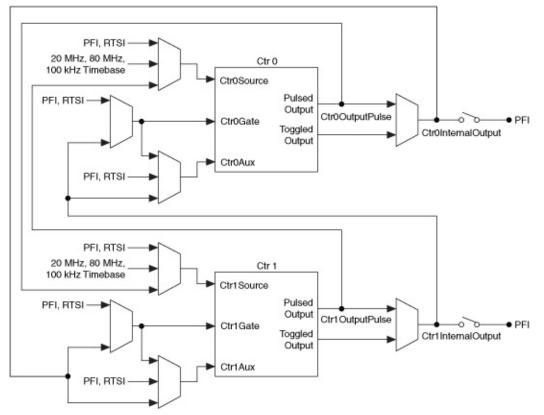

The following figure shows the internal routing for DAQ devices with the STC counter/timer such as E Series devices. The black circles represent terminals.

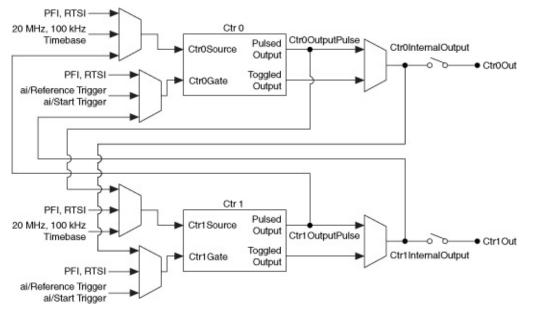

### C Series, M Series, and TIO Counter Internal Routing Diagram

The following figure shows the routing for DAQ devices that use the TIO counter/timer such as 66XX devices or for devices that use the STC2 timer, which is on M Series devices and the CompactDAQ chassis.

You can use any PFI line on your device. However, there are preferred PFI lines that do not require extra internal resources when used. Refer to Routing Considerations for Timing I/O Devices for additional information.

## **Duplicate Count Prevention**

Duplicate count prevention (or synchronous counting mode) ensures that a counter returns correct data in applications that use a slow or nonperiodic external source. Duplicate count prevention applies to any counter application such as measuring frequency or period. In such applications, the counter should store the number of times an external Source pulses between rising edges on the Gate signal.

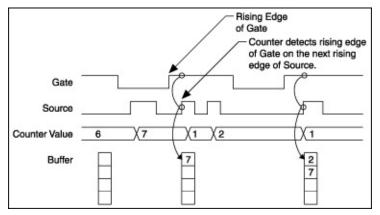

## Example Application That Works Correctly (No Duplicate Counting)

The following figure shows a buffered period measurement that uses an external signal as the Source.

On the first rising edge of the Gate, the current count of 7 is stored. On the next rising edge of the Gate, the counter stores a 2 since two Source pulses occurred after the previous rising edge of Gate.

The counter synchronizes or samples the Gate signal with the Source signal. So the counter does not detect a rising edge in the Gate until the next Source pulse. In this example, the counter stores the values in the buffer on the first rising Source edge after the rising edge of Gate.

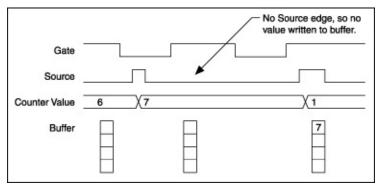

## Example Application That Works Incorrectly (Duplicate Counting)

In the following figure, after the first rising edge of Gate, no Source pulses occur. So the counter does not write the correct data to the buffer.

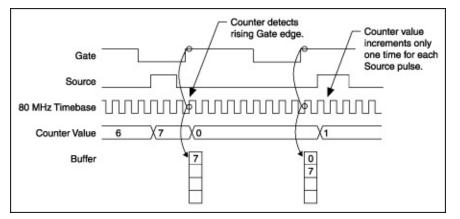

#### **Example Application That Prevents Duplicate Counting**

With duplicate count prevention enabled, the counter synchronizes both the Source and Gate signals to the maximum timebase. By synchronizing to the timebase, the counter detects edges on the Gate even if the Source does not pulse. This enables the correct current count to be stored in the buffer even if no Source edges occur in between Gate signals. Refer to the following example.

Even if the Source pulses are long, the counter increments only once for each Source pulse.

Normally, the counter value and Counter *n* Internal Output signals change synchronously to the Source signal. With duplicate count prevention, the counter value and Counter *n* Internal Output signals change synchronously to the maximum timebase.

#### When To Use Duplicate Count Prevention

You should use duplicate count prevention if the following conditions are true.

- You are making a counter measurement

- You are using an external signal (such as PFI *x*) as the counter Source

- The frequency of the external Source is 25% of your maximum timebase or less

- You can have counter value and output to change synchronously with the maximum timebase

In all other cases, you should *not* use duplicate count prevention.

#### Enabling and Disabling Duplicate Count Prevention in NI-DAQmx

NI-DAQmx enables duplicate count prevention by default except in the following cases:

- The input terminal is an onboard timebase.

- <u>Prescaling</u> is enabled.

- The timing type is on demand.

- The **Counter Output Event Output Terminal** attribute/property is used in your application.

You can enable and disable duplicate count prevention in NI-DAQmx with the **Enable Duplicate Count Prevention** attribute/property.

## Prescaling

Prescaling allows the counter to count a signal that is faster than the maximum timebase of the counter. The TIO counters offer 8X and 2X prescaling on each counter. You can disable prescaling. Each prescaler consists of a small, simple counter that counts to eight (or two) and rolls over. This counter is specifically designed for this application and can count signals that are faster than the general purpose counters. The Ctr*N*source signal on the general purpose counter is the divided signal from the simple counter.

Prescaling is for two-counter period and frequency measurements in which the measurement is made on a continuous, repetitive signal. The prescaling counter cannot be read; therefore, you cannot determine how many edges have occurred since the previous roll-over. Prescaling can be also used for counting edges provided it is acceptable to have an error of up to seven when using 8X prescaling or one when using 2X prescaling.

## Counter Input Error Reporting with M Series USB and C Series

With C Series and M Series USB devices (except <u>bus-powered M Series</u> <u>devices</u>), buffered counter input error reporting occurs every 128 samples for high-speed USB and every 16 samples for full-speed USB. When an error is detected, the task stops. To prevent the acquisition of incorrect samples, only data within either the 128- or 16-sample group is reported. For instance, if you attempt to acquire 256 samples, and an error occurs after sample 250, the task returns 128 samples instead of 249. If you attempt to acquire a number of samples less than or equal to 128 or 16 and an error occurs, the task returns no samples.

## **Digital Filtering**

Digital filtering rejects state transitions that do not stay at a state for a specified amount of time. For example, for an edge counting measurement with digital filtering, the device does not count an edge if the pulse width is not at least the specified time. For digital input tasks, the device does not recognize that a signal changed from one state to another unless the signal remains at that state for the specified amount of time.

This section contains information about digital filtering for <u>C Series</u>, <u>DIO</u>, <u>M Series</u>, and <u>TIO</u> devices.

# Digital Filtering Considerations for C Series and M Series Devices

Digital debouncing filters are only supported on counter inputs. Each PFI line can independently select from three fixed values (125 ns, 6.425 µs, 2.55 ms). For each counter input attribute/property, there are two attributes/properties associated with digital debounce filtering: **Digital Filter Enable** and **Digital Filter Minimum Pulse Width**.

When you set the **Digital Filter Enable** to true, you must also configure the **Digital Filter Minimum Pulse Width** attribute/property. This value represents the minimum value that is guaranteed to pass into the STC II. Refer to your device documentation to determine the minimum pulse width guaranteed to be blocked.

The following table lists the counter input terminals that can be digitally filtered.

| quency Input Terminal<br>od Input Terminal<br>nt Edges Input Terminal<br>nt Edges Count Direction<br>ition A Input Terminal |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| nt Edges Input Terminal<br>nt Edges Count Direction<br>ition A Input Terminal                                               |  |  |

| nt Edges Count Direction<br>ition A Input Terminal                                                                          |  |  |

| ition A Input Terminal                                                                                                      |  |  |

| •                                                                                                                           |  |  |

|                                                                                                                             |  |  |

| ition B Input Terminal                                                                                                      |  |  |

| Position Z Input Terminal                                                                                                   |  |  |

| Pulse Width Input Terminal                                                                                                  |  |  |

| -Edge First Input Terminal                                                                                                  |  |  |

| -Edge Second Input Terminal                                                                                                 |  |  |

| ni-Period Input Terminal                                                                                                    |  |  |

| nter Input Timebase Source                                                                                                  |  |  |

| nter Output Timebase Source                                                                                                 |  |  |

| nple Clock Source                                                                                                           |  |  |

| Start Trigger Source                                                                                                        |  |  |

| <u> </u>                                                                                                                    |  |  |

|                                                                                                                             |  |  |

Arm Start Trigger Source

## **Digital Filtering Considerations for DIO Devices**

Digital filtering is enabled by default on all isolated DIO devices that support digital filtering. The default minimum pulse width is 0.1 ms or 100  $\mu$ s. Refer to the following table for a list of devices and their digital filtering settings.

| PCI-6510 |

|----------|

| J        |

| PCI-6511 |

| PCI-6514 |

| PCI-6515 |

| PCI-6518 |

| PCI-6519 |

| PCI-6527 |

| PCI-6528 |

| PXI-6511 |

| PXI-6514 |

| PXI-6515 |

| PXI-6527 |

| PXI-6528 |

| PXI-6529 |

| PCI-6509 |

| PXI-6509 |

|          |

| Digital Filtering Not Supported | NI PCI-6503   |

|---------------------------------|---------------|

|                                 | NI PCI-6512   |

|                                 | NI PCI-6513   |

|                                 | NI PCI-6516   |

|                                 | NI PCI-6517   |

|                                 | NI PCI-DIO-96 |

|                                 | NI PXI-6508   |

|                                 | NI PXI-6512   |

|                                 | NI PXI-6513   |

|                                 | NI USB-6501   |

# Digital Filtering Considerations for TIO-Based Devices

There are two methods for filtering and synchronizing digital signals. One method is to synchronize the input signal to the maximum onboard timebase on the device. To do this, set **Digital Synchronization Enable** to true.

The other method is to pass the input of any PFI line through a digital debouncing filter. Each PFI line can independently select from four fixed values (5  $\mu$ s, 1  $\mu$ s, 500 ns, 100 ns) and one custom filter value. The custom filter value must be the same for each PFI line. That is, if you choose a filter value of 2  $\mu$ s for a PFI line, other PFI lines on the device at the same time can only choose from the four fixed values and the 2  $\mu$ s value selected as the custom filter value. For each counter input property, there are four attributes/properties associated with digital debounce filtering: **Digital Filter Enable**, **Digital Filter Minimum Pulse Width**, **Digital Filter Timebase Source**, and **Digital Filter Timebase Rate**.

When you set the **Digital Filter Enable** to true, you must also configure the **Digital Filter Minimum Pulse Width** attribute/property. This value represents the minimum value that is guaranteed to pass into the TIO. The minimum pulse width guaranteed to be blocked is one-half of the **Digital Filter Minimum Pulse Width** attribute/property. When you select a custom filter value with the **Minimum Pulse Width** attribute/property, NI-DAQmx uses an internal 32-bit utility counter to generate the desired filter value. If you would like to generate the filter clock using your own external signal, you can use the **Digital Filter Timebase Source** and **Digital Filter Timebase Rate** attributes/properties. You must configure both to use an external signal as the source for the digital filter.

You cannot set both **Digital Filter Enable** and **Digital Synchronization Enable** to true at the same time. You can use only one of these digital filtering methods at a time.

The following table lists the counter input terminals that can be digitally filtered.

| Туре    | Attribute/Property       |  |

|---------|--------------------------|--|

| Channel | Frequency Input Terminal |  |

|         | Period Input Terminal    |  |

|            | Count Edges Input Terminal     |  |  |  |  |  |  |

|------------|--------------------------------|--|--|--|--|--|--|

|            | Count Edges Count Direction    |  |  |  |  |  |  |

|            | Position A Input Terminal      |  |  |  |  |  |  |

|            | Position B Input Terminal      |  |  |  |  |  |  |

|            | Position Z Input Terminal      |  |  |  |  |  |  |

|            | Pulse Width Input Terminal     |  |  |  |  |  |  |

|            | Two-Edge First Input Terminal  |  |  |  |  |  |  |

|            | Two-Edge Second Input Terminal |  |  |  |  |  |  |

|            | Semi-Period Input Terminal     |  |  |  |  |  |  |

|            | Counter Input Timebase Source  |  |  |  |  |  |  |

|            | Counter Output Timebase Source |  |  |  |  |  |  |

| Timing     | Sample Clock Source            |  |  |  |  |  |  |

| Triggering | Start Trigger Source           |  |  |  |  |  |  |

|            | Pause Trigger Source           |  |  |  |  |  |  |

|            | Arm Start Trigger Source       |  |  |  |  |  |  |

# Digital I/O

This section contains information specific to DIO devices.

## **Change Detection**

This section contains information about change detection for <u>C Series</u>, <u>DIO</u>, and <u>M Series</u> devices.

## Change Detection Considerations for NI 6527 Devices

The **Change Detection Overflowed** attribute/property uses the change detection overflow circuitry on a DIO device to determine if an overflow occurred. The NI 6527 change detection overflow circuitry does not detect an overflow if a single rising edge and a single falling edge are detected prior to reading a sample. It will detect overflows if two rising edges or two falling edges occur prior to reading a sample.

## **Change-Detection Considerations for C Series and M Series Devices**

When performing a buffered change-detection task with an M Series device or a CompactDAQ system, the correlated digital input circuitry is automatically reserved and used for the task. Non-buffered tasks, including hardware-timed single point, do not reserve or use the correlated digital input circuitry.

## **Digital I/O Considerations for C Series Devices**

Digital I/O module capabilities depend on the type of digital signals that the module can measure or generate. Static digital I/O modules are designed for signals that change slowly and are accessed by softwaretimed reads and writes. Static digital I/O modules might take longer to update than their specifications indicate. Correlated digital I/O modules are for signals that change rapidly and are updated by either software or hardware-timed reads and writes. In addition, correlated digital I/O modules can perform the following tasks:

- Hardware-timed digital input/output tasks (when used in slots 1 through 4)

- Counter/timer tasks (when used in slots 5 and 6)

- Accessing PFI signal tasks (when used in slots 5 and 6)

The NI 9403, NI 9425, NI 9476, and NI 9477 are static digital I/O modules. The NI 9401, NI 9402, NI 9411, NI 9421, NI 9422, NI 9423, NI 9435, NI 9472, NI 9474, NI 9481, and NI 9485 are correlated digital I/O modules.

# Sample Clock Timing for Digital I/O

You can use sample clock timing for digital I/O on the following devices.

# AO Series<sup>1</sup>

• NI 673X

## $C Series^1$

Correlated digital I/O devices support sample clock timing as long as you use slots 1, 2, 3, or 4. Refer to <u>Digital I/O Considerations for C Series</u> for more information.

## M Series<sup>1</sup>

- NI 622X

- NI 625X

- NI 628X

# S Series $^{1}$

- NI 6115

- NI 6120

- NI 6132

- NI 6133

#### NI 653X

- NI PCI-6533 (DIO-32HS)

- NI PCI-6534

- NI PXI-6533

- NI PXI-6534

<sup>1</sup>There is no dedicated onboard sample clock for digital I/O on these devices. You must use a different clock, typically the AI or AO Sample Clock.

## Handshake Timing Devices

You can use handshake timing for digital I/O on the following devices:

- NI PCI-6025E

- NI PCI-6533 (DIO-32HS)

- NI PCI-6534

- NI PCI-DIO-24

- NI PCI-DIO-96

- NI PXI-6025E

- NI PXI-6508

- NI PXI-6533

- NI PXI-6534

- NI PCIe-6536

- NI PCIe-6537

## Burst Handshaking Timing Defaults for NI 653X Devices

The following table lists the default terminals used for burst handshake timing.

Note The NI 6533 and NI 6534 have two timing engines, Timing Engine 1 and Timing Engine 0. Each timing engine is associated with PFI lines. The timing engine you use is determined by the digital lines you use. If the least significant port is port 0, NI-DAQmx picks Timing Engine 0. If the least significant port is port 2, NI-DAQmx picks Timing Engine 1.

| Device                    | Pause Trigger Default                               | Ready for Transfer Event<br>Default                 |

|---------------------------|-----------------------------------------------------|-----------------------------------------------------|

| NI PCI-6533<br>(DIO-32HS) | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PCI-6534               | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PXI-6533               | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PXI-6534               | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PCIe-6536              | PFI 0                                               | PFI 1                                               |

| NI PCIe-6537              | PFI 0                                               | PFI 1                                               |

The recommended sample clock terminal for burst handshake timing is PFI 4 (Timing Engine 0) or PFI 5 (Timing Engine 1).

# Burst Handshake Timing for Digital I/O

You can use burst handshake timing for digital I/O on the following devices:

- NI PCI-6533 (DIO-32HS)

- NI PCI-6534

- NI PXI-6533

- NI PXI-6534

- NI PCIe-6536

- NI PCIe-6537

# Handshake Timing Defaults

The following table lists the default terminals used for handshake timing for NI 653X devices.

**Note** The NI 6533 and NI 6534 have two timing engines, Timing Engine 1 and Timing Engine 0. Each timing engine is associated with PFI lines. The timing engine you use is determined by the digital lines you use. If the least significant port is port 0, NI-DAQmx picks Timing Engine 0. If the least significant port is port 2, NI-DAQmx picks Timing Engine 1.

| Device                    | Handshake Trigger<br>Default                        | Handshake Event Default                             |

|---------------------------|-----------------------------------------------------|-----------------------------------------------------|

| NI PCI-6533<br>(DIO-32HS) | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PCI-6534               | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PXI-6533               | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PXI-6534               | PFI 2 (Timing Engine 0),<br>PFI 3 (Timing Engine 1) | PFI 6 (Timing Engine 0),<br>PFI 7 (Timing Engine 1) |

| NI PCIe-6536              | PFI 0                                               | PFI 1                                               |

| NI PCIe-6537              | PFI 0                                               | PFI 1                                               |

The recommended sample clock terminal for burst handshake timing is PFI 4 (Timing Engine 0) or PFI 5 (Timing Engine 1).

$<sup>\</sup>overline{\mathbb{N}}$

## Watchdog Timers

Watchdog timers are a hardware feature that you can use to detect a failure in the software controlling the device. Software failures could include a system crash or a loop rate that is slower than you intend. To use a watchdog timer, you must use a watchdog timer task. When you create a watchdog timer task, you specify the timeout value for the watchdog timer and a set of expiration states for digital output physical channels on the device. The channels go to those expiration states if the watchdog timer expires.

Your application must continuously reset the watchdog timer to prevent it from expiring. For example, if you have a digital I/O application, and you expect a loop in the application to acquire and analyze data 10 times per second, you should set the watchdog timer to expire in 100 ms and reset the timer inside the digital I/O loop. If the loop does not execute once every 100 ms, the watchdog timer expires and the device goes into the expired state. You must then clear the expiration or reset the device.

Also, you can use the Expiration Trigger to cause the watchdog timer to expire. Set the timeout of the watchdog timer task to -1 to disable expiration due to timeout if you want the Expiration Trigger to be the only mechanism to cause expiration.

# **Pause Triggering**

This section contains information about Pause Triggering for <u>AO Series</u>, <u>DSA</u>, <u>E Series</u>, <u>M Series</u>, <u>S Series</u>, and <u>TIO</u> devices.

# Pause Trigger Considerations for AO Series Devices

The source of your sample clock can affect when your generation resumes after the deassertion of a Pause Trigger.

### **Analog Output**

When you generate analog output signals, the generation pauses as soon as the Pause Trigger is asserted. If the source of your sample clock is the onboard clock, the generation resumes as soon as the Pause Trigger is deasserted.

|               |   |  | 1 |

|---------------|---|--|---|

| Pause Trigger |   |  |   |

| Sample Clock  | Л |  |   |

|               |   |  |   |

If you are using any signal other than the onboard clock as the source of your sample clock, the generation resumes as soon as the Pause Trigger is deasserted and another edge of the sample clock is received, as shown in the following figure.

| Pause Trigger |     | - |   | Ť. |  |

|---------------|-----|---|---|----|--|

| Sample Clock  | _1_ |   | 1 |    |  |

#### Counters

Continuous pulse-train generation: The pulse-train generation pauses as soon as the Pause Trigger is asserted, not at the end of a pulse. The pulse train resumes after the Pause Trigger is deasserted. A Pause Trigger elongates either the high or low pulse depending on which one was being generated at the time the Pause Trigger was asserted.

| Pause Trigger |     | H | Ŀ |

|---------------|-----|---|---|

| Pulse Train   | ллı |   | л |

Nonbuffered edge counting: The counter stops counting edges as soon as the Pause Trigger is asserted and resumes counting edges after the Pause Trigger is deasserted.

| Pause Trigger  | _ |     |      | -i |            |

|----------------|---|-----|------|----|------------|

| Counter Source | f | LFL | лцғи | L  | _ <b>≜</b> |

| Counter Value  | 1 | 2   | 3    | 4  | 5          |

# Pause Trigger Considerations for DSA Devices

DSA devices do not support Pause Triggering.

# Pause Trigger Considerations for E Series and M Series Devices