## **MPASM Assembler Overview**

An overview of MPASM assembler and its capabilities is presented.

- What is MPASM Assembler

- Assembler Migration Path

- <u>Assembler Compatibility Issues</u>

- How MPASM Assembler Helps You

#### What is MPASM Assembler

MPASM assembler (the assembler) is a command-line or Windows-based PC application that provides a platform for developing assembly language code for Microchip's PICmicro microcontroller (MCU) families. Generically, MPASM assembler will refer to the entire development platform including the macro assembler and utility functions.

MPASM assembler supports all PICmicro MCU, memory, and secure data (KeeLoq)) products from Microchip Technology Inc.

Microchip Technology Inc.

Microchip's Web Site Voice: (480) 792-7200 Fax: (480) 899-9210 Microchip's E-mail Address

#### **Assembler Migration Path**

Since MPASM assembler is a universal assembler for all PICmicro MCU devices, an application developed for the PIC16C54 can be easily translated into a program for the PIC16C71. This would require changing the instruction mnemonics that are not the same between the devices (assuming that register and peripheral usage were similar). The rest of the directive and macro language will be the same.

#### **Assembler Compatibility Issues**

MPASM assembler is compatible with all Microchip PICmicro MCU development systems currently in production. This includes MPLAB SIM (PICmicro MCU discrete-event simulator), MPLAB ICE 2000 (PICmicro MCU in-circuit emulator), MPLAB ICD 2 (incircuit debugger - PIC18 parts), PRO MATE II (device programmer) and PICSTART Plus (low-cost development programmer).

MPASM assembler supports a clean and consistent method of specifying radix. You are encouraged to develop new code using the methods described within this document, even though certain older syntaxes may be supported for compatibility reasons.

#### **How MPASM Assembler Helps You**

MPASM assembler provides a universal solution for developing assembly code for all of Microchip's 12-bit, 14-bit, 16-bit, and Enhanced 16-bit core PICmicro MCUs. Notable features include:

- All PICmicro MCU Instruction Sets

- Command Line Interface

- Command Shell Interfaces

- Rich Directive Language

- Flexible Macro Language

- MPLAB IDE Compatibility

#### Microchip Technology Inc.

<u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

## Getting Started with MPASM Assembler

An overview of assembler (MPASM assembler) operation and instructions for the installation of MPASM assembler on your system is shown.

- Overview of Assembler

- Assembler Input/Output Files

- Assembler Installation

#### **Overview of Assembler**

MPASM assembler can be used in two ways:

To generate absolute code that can be executed directly by a microcontroller.

To generate object code that can be linked with other separately assembled or compiled modules.

#### **Generating Absolute Code**

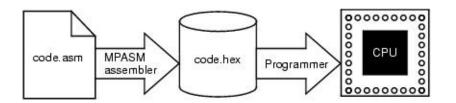

Absolute code is the default output from MPASM assembler. This process is shown below.

When a source file is assembled in this manner, all values used in the source file must be defined within that source file, or in files that have been explicitly included. If assembly proceeds without errors, a HEX file will be generated, containing the executable machine code for the target device. This file can then be used in conjunction with a device programmer to program the microcontroller.

#### **Generating Object Code**

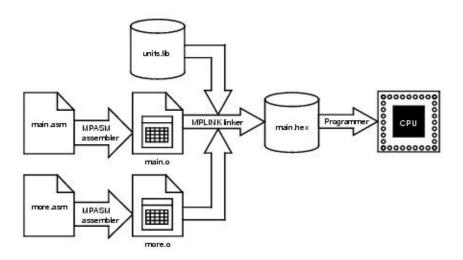

MPASM assembler also has the ability to generate an object module that can be linked with other modules using Microchip's MPLINK linker to form the final executable code. This method is very useful for creating reusable modules that do not have to be retested each time they are used.

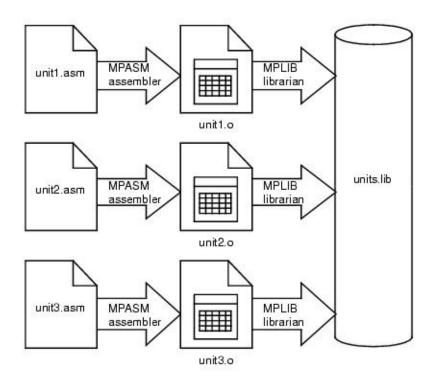

Related modules can also be grouped and stored together in a library using Microchip's MPLIB librarian. Required libraries can be specified at link time, and only the routines that are needed will be included in the final executable.

Refer to Relocatable Objects for more information on the

differences between absolute and object assembly.

## **Assembler Input/Output Files**

These are the default file extensions used by the assembler and the associated utility functions.

#### **TABLE: INPUT FILES**

Source Code (.asm)Default source file extension input to assembler.Include File (.inc)Include (header) file

#### **TABLE: OUTPUT FILES**

| Listing File (.lst)                            | Default output extension for listing files generated by assembler.                                       |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| <u>Error File (.err)</u>                       | Output extension from assembler for error files.                                                         |

| <u>Hex File Formats (.hex,<br/>.hxl, .hxh)</u> | Output extension from assembler for hex files.                                                           |

|                                                | Output extension for the symbol and debug file. This file may be output from assembler or MPLINK linker. |

| <u>Object File (.o)</u>                        | Output extension from assembler for object files.                                                        |

#### Source Code (.asm)

Assembly source code is one programming language you may use to develop your application. The source code file may be created using any ASCII text file editor. It should conform to the following basic guidelines.

Each line of the source file may contain up to four types of information:

- Labels

- <u>Mnemonics</u>

- Operands

- <u>Comments</u>

The order and position of these are important. Labels must start in column one. Mnemonics may start in column two or beyond.

Operands follow the mnemonic. Comments may follow the operands, mnemonics or labels, and can start in any column. The maximum column width is 255 characters.

Whitespace or a colon must separate the label and the mnemonic, and the mnemonic and the operand(s). Multiple operands must be separated by a comma.

# Sample MPASM Assembler Source Code (Shows multiple operands)

; ; Sample MPASM Source Code. For illustration only. ; list p=16c54 Dest equ H'0B' org H'01FF' goto Start org H'0000' Start movlw H'0A' movwf Dest bcf Dest, 3 goto Start end

#### Labels

A label must start in column 1. It may be followed by a colon (:), space, tab or the end of line.

Labels must begin with an alpha character or an under bar (\_) and may contain alphanumeric characters, the under bar and the question mark.

**Note:** Do not use labels with a leading underscore and number, e.g., \_2NDLOOP. Also, do not use the assembler reserved word Halt as a label.

Labels may be up to 32 characters long. By default they are case sensitive, but case sensitivity may be overridden by a command line option. If a colon is used when defining a label, it is treated as a label operator and not part of the label itself.

#### **Mnemonics**

Assembler instruction mnemonics, assembler directives and macro calls must begin in column two or greater. If there is a label on the same line, instructions must be separated from that label by a colon, or by one or more spaces or tabs.

#### **Operands**

Operands must be separated from mnemonics by one or more spaces, or tabs. Multiple operands must be separated by commas.

#### Comments

MPASM assembler treats anything after a semicolon as a comment. All characters following the semicolon are ignored through the end of the line. String constants containing a semicolon are allowed and are not confused with comments.

#### Include File (.inc)

Assembler include, or header, file. Usually contains device-specific register and bit assignments.

As an example, to add the standard header file for the PIC18F452 device to your assembly code, use:

```

#include <p18f452.inc>

```

## Listing File (.lst)

A listing file provides a mapping of source code to machine instructions. MPASM assembler and MPLINK linker can generate listing files.

#### Sample MPASM Assembler Listing File

The product name and version, the assembly date and time, and the page number appear at the top of every page.

The first column of numbers contains the base address in memory where the code will be placed. The second column displays the 32bit value of any symbols created with the SET, EQU, VARIABLE, CONSTANT, or CBLOCK directives. The third column is reserved for the machine instruction. This is the code that will be executed by the PICmicro MCU. The fourth column lists the associated source file line number for this line. The remainder of the line is reserved for the source code line that generated the machine code.

Errors, warnings, and messages are embedded between the source lines and pertain to the following source line.

The symbol table lists all symbols defined in the program. The memory usage map gives a graphical representation of memory usage. 'X' marks a used location and '-' marks memory that is not used by this object. The memory map is not printed if an object file is generated.

MPASM 01.99.21 Intermediate MANUAL.ASM 5-30-1997 15:31:05 PAGE 1 LOC OBJECT CODE LINE SOURCE TEXT VALUE 00001 ; 00002 ; Sample MPASM Source Code. For illustration only. 00003 ;

00004 list p=16c54 0000000B 00005 Dest equ H'0B' 00006 01FF 00007 org H'01FF' 01FF 0A00 00008 goto Start 00009 0000 00010 org H'0000' 00011 0000 0C0A 00012 Start movlw H'0A' 0001 002B 00013 movwf Dest 0002 0A00 00014 goto Start 00015 00016 end MPASM 01.99.21 Intermediate MANUAL.ASM 5-30-1997 15:31:05 PAGE 2 SYMBOL TABLE LABEL VALUE Dest 000000B Start 00000000 16C54 0000001 MEMORY USAGE MAP ('X' = Used, '-' = Unused) 0000 : XXX------01C0 : -----X All other memory blocks unused. Program Memory Words Used: 4 Program Memory Words Free: 508 Errors: 0 Warnings : 0 reported, 0 suppressed Messages : 0 reported, 0 suppressed

## **Error File (.err)**

MPASM assembler, by default, generates an error file. This file can be useful when debugging your code. The MPLAB IDE Source Level Debugger will automatically open this file in the case of an error. The format of the messages in the error file is: <type>[<number>] <file> <line> <description>

For example:

Error[113] C:\PROG.ASM 7 : Symbol not previously defined (start)

The error file will contain MPASM assembler errors, warnings and messages.

## Hex File Formats (.hex, .hxl, .hxh)

MPASM Assembler is capable of producing different hex file formats.

| Format Name            | Format Type | File Extension | Use                          |

|------------------------|-------------|----------------|------------------------------|

| Intel Hex Format       | INHX8M      | .HEX           | for standard programmers     |

| Intel Split Hex Format | INHX8S      | .HXL, .HXH     | for odd/even ROM programmers |

| Intel Hex 32 Format    | INHX32      | .HEX           | for 16-bit core programmers  |

#### **Intel Hex Format**

This format produces one 8-bit hex file with a low byte, high byte combination. Since each address can only contain 8 bits in this format, all addresses are doubled. This file format is useful for transferring PICmicro MCU series code to PRO MATE II, PICSTART Plus and third party PICmicro MCU programmers.

Each data record begins with a 9-character prefix and ends with a 2-character checksum. Each record has the following format:

:ВВААААТТНННН....НННСС

where:

BB - is a two digit hexadecimal byte count representing the number of data bytes that will appear on the line.

AAAA - is a four digit hexadecimal address representing the starting address of the data record.

TT - is a two digit record type record type that will always be '00' except for the end-of-file record, which will be '01'.

HH - is a two digit hexadecimal data byte, presented in lowbyte/high-byte combinations.

CC - is a two digit hexadecimal checksum that is the two's complement of the sum of all preceding bytes in the record.

Example

#### Intel Split Hex Format

The split 8-bit file format produces two output files: .HXL and .HXH. The format is the same as the normal 8-bit format, except that the low bytes of the data word are stored in the .HXL file, and the high bytes of the data word are stored in the .HXH file, and the addresses are divided by two. This is used to program 16-bit words into pairs of 8-bit EPROMs, one file for Low Byte, one file for High Byte.

Example

<file\_name>.HXL

#### **Intel Hex 32 Format**

The extended 32-bit address hex format is similar to the hex 8 format, except that the extended linear address record is output also to establish the upper 16 bits of the data address. This is mainly used for 16-bit core devices since their addressable program memory exceeds 32 kwords.

Each data record begins with a 9-character prefix and ends with a 2-character checksum. Each record has the following format:

:BBAAAATTHHHH....HHHCC

where:

BB - is a two digit hexadecimal byte count representing the number of data bytes that will appear on the line.

AAAA - is a four digit hexadecimal address representing the starting address of the data record.

- TT is a two digit record type:

- 00 Data record

- 01 End of File record

- 02 Segment address record

- 04 Linear address record

HH - is a two digit hexadecimal data byte, presented in low byte, high byte combinations.

CC - is a two digit hexadecimal checksum that is the two's complement of the sum of all preceding bytes in the record.

#### Symbol and Debug File (.cod)

A COD file is used by MPLAB IDE to debug code. The COD file name, including the path, has a 63 character limit. MPASM assembler and MPLINK linker can generate a COD file.

## **Object File (.0)**

Object files are the relocatable code produced from source files.

• MPASM assembler assembles source files into object files.

• MPLINK linker combines object files and library files, according to a linker script, into a single output file.

• MPLIB librarian combines several object files into a single library file.

< >

#### **Assembler Installation**

When MPLAB IDE is installed, the windowed version of MPASM assembler is also installed. You may obtain the MPLAB IDE software either from the latest MPLAB IDE CD-ROM or from our web site.

Actually, there are two versions of MPASM assembler:

- a Windows version, MPASMWIN.EXE (Recommended)

- a DOS version, MPASM.EXE, for DOS 5.0 or greater

#### **Available free with MPLAB IDE**

MPASMWIN.EXE has a Windows shell interface. MPASMWIN.EXE may be used with Windows 95/98/ME, Windows NT/2000 or Windows XP. You can use this version with MPLAB IDE (recommended) or stand-alone.

#### Available free with MPLAB C1X compilers

MPASM.EXE has a command line interface. MPASM.EXE may be used with DOS or a DOS window in Windows 3.x, Windows 95/98/ME, Windows NT/2000 or Windows XP. You can use it with MPLAB IDE, though MPASMWIN.EXE is recommended.

## **Assembler Usage with MPLAB IDE**

How to use MPASM assembler with MPLAB IDE v6.xx and later is discussed here. The windows version (mpasmwin.exe) of the assembler should be used with MPLAB IDE.

- MPLAB IDE Interface

- MPLAB IDE Projects

- Project and Assembler Setup

#### Microchip Technology Inc.

Microchip's Web Site Voice: (480) 792-7200 Fax: (480) 899-9210 Microchip's E-mail Address

#### **MPLAB IDE Interface**

MPASM assembler may be used with the MPLAB IDE integrated development environment to provide GUI development of your application. In order to use MPASM assembler with MPLAB IDE, you must first install MPLAB IDE. The latest version of this free software is available at our website (http://www.microchip.com) or from any sales office (back cover). When you install MPLAB IDE, you will be installing MPASM assembler as well.

Once MPLAB IDE is installed on your PC, check the settings below to ensure that the assember is installed properly as a language tool.

1. From the MPLAB IDE menu bar, select <u>Project>Set Language</u> <u>Tool Locations</u> to open a dialog to set/check language tool executable location.

# FIGURE: MPASM ASSEMBLER EXECUTABLE LOCATION

| E IAR Systems PIC18 Toolsuite<br>Microchip ASM30 Toolsuite<br>Microchip C17 Toolsuite<br>Microchip C18 Toolsuite<br>Microchip C30 Toolsuite<br>Microchip C30 Toolsuite | icrochip ASM30 Toolsuite<br>icrochip C17 Toolsuite<br>icrochip C18 Toolsuite<br>icrochip C30 Toolsuite<br>icrochip MPASM Toolsuite<br>Executables<br>MPASM Assembler (mpasmwin.exe)<br>MPLINK Object Linker (mplink.exe) | IAR Systems Midran                         |                                | <b>^</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------|----------|

| e Microchip C17 Toolsuite<br>Microchip C18 Toolsuite<br>e Microchip C30 Toolsuite                                                                                      | icrochip C17 Toolsuite<br>icrochip C38 Toolsuite<br>icrochip C30 Toolsuite<br>icrochip MPASM Toolsuite<br>Executables<br>MPASM Assembler (mpasmwin.exe)<br>MPLINK Object Linker (mplink.exe)                             |                                            |                                |          |

| e Microchip C18 Toolsuite<br>e Microchip C30 Toolsuite                                                                                                                 | icrochip C18 Toolsuite<br>icrochip C30 Toolsuite<br>icrochip MPASM Toolsuite<br>Executables<br>MPASM Assembler (mpasmwin.exe)<br>MPLINK Object Linker (mplink.exe)                                                       |                                            |                                |          |

| ∋ Microchip C30 Toolsuite                                                                                                                                              | icrochip C30 Toolsuite<br>icrochip MPASM Toolsuite<br>Executables<br>MPASM Assembler (mpasmwin.exe)<br>MPLINK Object Linker (mplink.exe)                                                                                 |                                            |                                |          |

|                                                                                                                                                                        | icrochip MPASM Toolsuite<br>= Executables<br>MPASM Assembler (mpasmwin.exe)<br>                                                                                                                                          |                                            |                                |          |

| - MICTOCHID MEASM LOOISUILE                                                                                                                                            | - Executables<br>MPASM Assembler (mpasmwin.exe)<br>MPLINK Object Linker (mplink.exe)                                                                                                                                     |                                            |                                |          |

|                                                                                                                                                                        | -                                                                                                                                                                                                                        | <mark>MPASM Ass</mark><br><b>MPLINK Ob</b> | ject Linker (mplink.exe)       | -        |

| peation                                                                                                                                                                |                                                                                                                                                                                                                          |                                            | BIDE\MCHIP Tools\mpasmwin exe  | Browse   |

| cation                                                                                                                                                                 |                                                                                                                                                                                                                          |                                            | B IDE\MCHIP_Tools\mpasmwin.exe | Browse.  |

- 1. In the dialog, under Registered Tools, select "Microchip MPASM Toolsuite". Click the "+" to expand.

- Select Executables. Click the "+" to expand.

• Select MPASM Assembler (mpasmwin.exe). Under Location, a path to the mpasmwin.exe file should be displayed. If no path is displayed, enter one or browse to the location of this file. By default, it is located at:

C:\Program Files\MPLAB IDE\MCHIP\_Tools\mpasmwin.exe

• Click OK.

#### **MPLAB IDE Projects**

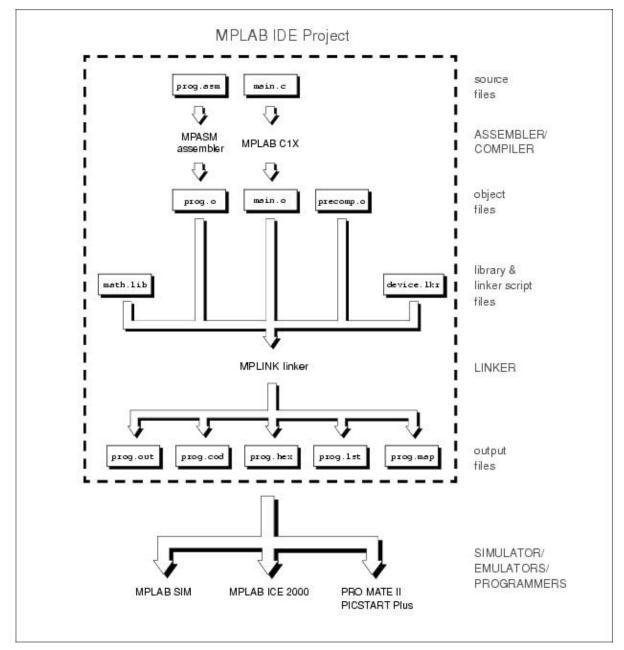

A project in MPLAB IDE is a group of files needed to build an application, along with their associations to various build tools. Below a generic MPLAB IDE Project using the MPASM assembler tool is shown.

#### FIGURE: PROJECT RELATIONSHIPS

In this MPLAB IDE Project, an assembly source file (prog.asm) is shown with its associated assembler (MPASM assembler). MPLAB IDE will use this information to generate the object file prog.o for input into MPLINK linker.

The C source file main. c is also shown with its associated MPLAB C1X compiler. MPLAB IDE will use this information to generate an object file (main.0) for input into the linker (MPLINK linker). See either the MPLAB C17 Compiler User's Guide (DS51290) for PIC17CXXX devices or the MPLAB C18 Compiler User's Guide (DS51288) for PIC18XXXXX devices for more information on using these compilers.

In addition, precompiled object files (precomp.o) may be included in a project, with no associated tool required. Types of precompiled object files that are generally required in a project are:

- Start up code

- Initialization code

- Interrupt service routines

- Register definitions

Precompiled object files are often device and/or memory model dependent. For more information on available Microchip precompiled object files, see either the *MPLAB C17 Compiler Libraries* (DS51296) for PIC17CXXX devices or the *MPLAB C18 Compiler Libraries* (DS51297) for PIC18XXXXX devices.

Some library files (math.lib) are available with the compiler. Others may be built outside the project using the librarian tool (MPLIB librarian). See the MPLIB Object Librarian section later in this manual for more information on using the librarian. For more information on available Microchip libraries, see the MPLAB C1X library documents previously mentioned. The object files, along with library files and a linker script file (device.lkr) are used to generate the project output files via the linker (MPLINK linker). See the MPLINK Object Linker section later in this manual for more information on linker script files and using the linker.

The main output file generated by MPLINK linker is the **Hex file** (prog.hex), used by simulators (MPLAB SIM), emulators (MPLAB ICE 2000) and programmers (PRO MATE II and PICSTART Plus). The other output files are:

- **COFF file (.out).** Intermediate file used by MPLINK linker to generate Code file, Hex file, and Listing file.

- Code file (.cod). Debug file used by MPLAB IDE.

- Listing file (.lst). Original source code, side-by-side with final binary code.

- **Map file (.map).** Shows the memory layout after linking. Indicates used and unused memory regions.

< >

#### **Project and Assembler Setup**

To set up an MPLAB IDE project for the first time, it is advisable to use the built-in Project Wizard (*Project>Project Wizard*.) In this wizard, you will be able to select a language toolsuite that uses MPASM assembler, e.g., the Microchip MPASM Toolsuite. For more on the wizard, and MPLAB IDE projects, see MPLAB IDE documentation.

Once you have a project set up, you may then set up properties of MPASM assembler in MPLAB IDE.

From the MPLAB IDE menu bar, select <u>Project>Build</u> <u>Options>Project</u> to open a dialog to set/check project build options.

**Note:** MPASM assembler does not recognize include path information specified in MPLAB IDE.

• Click on the MPASM Assembler tab and enter/change assembler settings.

# Assembler Usage without MPLAB IDE

How to use MPASM assembler without MPLAB IDE is discussed here.

The command-line version (**mpasm.exe**) may be run from the command line or a command shell. The windows version (**mpasmwin.exe**) may be from the command line or a Windows shell.

- Command Line Interface

- Command Shell Interface

- Windows Shell Interface

- Troubleshooting

#### Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200

Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

#### **Command Line Interface**

MPASM assembler can be invoked through the command line interface (command prompt) as follows:

```

mpasmwin [/<Option>[ /<Option>...]] [<filename>]

```

or

```

mpasm [/<Option>[ /<Option>...]] [<filename>]

```

where

/<0ption> - refers to one of the command line options

<filename> - is the file being assembled

For example, if test.asm exists in the current directory, it can be assembled with following command:

mpasmwin /e /l test

The assembler defaults (noted below) can be overridden with options:

| Option               | Result                                                                          |

|----------------------|---------------------------------------------------------------------------------|

| / <option></option>  | Enables the option                                                              |

| / <option>+</option> | Enables the option                                                              |

| / <option>-</option> | Disables the option                                                             |

|                      | If appropriate, enables the option and directs the output to the specified file |

If the source filename is omitted, the appropriate shell interface is invoked, i.e.,

• mpasmwin - a Windows interface is displayed, which includes a Help button

mpasm - the assembler help panel is displayed (same as mpasm /?)

| Option | Default  | Description                                                                                                                                                             |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ?      | N/A      | Displays the assembler help panel (mpasm.exe).                                                                                                                          |

| а      | INHX8M   | Generate absolute .cod and .hex output directly from assembler; /a <hex-format>, where <hex-format> is one of [INHX8M   INHX8S   INHX32].</hex-format></hex-format>     |

| С      | On       | Enables/Disables case sensitivity.                                                                                                                                      |

| d      | N/A      | Define a text string substitution; /d <label>[=<value>].</value></label>                                                                                                |

| e      | On       | Enable/Disable/Set Path for error file.<br>/e Enable<br>/e- Disable<br>/e <path>error.file Enables/sets path</path>                                                     |

| h      | N/A      | Displays the assembler help panel.                                                                                                                                      |

| l      | On       | Enable/Disable/Set Path for list file<br>/l Enable<br>/l+ Enable<br>/l - Disable<br>/l <path>list.file Enables/sets path</path>                                         |

| m      | On       | Enable/Disable macro expansion.                                                                                                                                         |

| 0      | Off      | Enable/Disable/Set Path for object file.<br>/o Enable<br>/o+ Enable<br>/o- Disable<br>/o <path>object.file Enables/sets path</path>                                     |

| р      | None     | Set the processor type; /p <processor_type>, where <processor_type><br/>is a PICmicro MCU device, e.g., PIC16C54.</processor_type></processor_type>                     |

| q      | Off      | Enable/Disable quiet mode (suppress screen output).                                                                                                                     |

| r      | Hex      | Defines default radix; /r <radix>, where <radix> is one of [ HEX   DEC   OCT ].</radix></radix>                                                                         |

| t      | 8        | List file tab size; /t <size>.</size>                                                                                                                                   |

| w      | 0        | Set message level; /w <value>, where <value> is one of [0 1 2].<br/>0 all messages<br/>1 errors and warnings<br/>2 errors only</value></value>                          |

| x      | Off      | Enable/Disable/Set Path for cross reference file.<br>/x Enable<br>/x+ Enable<br>/x- Disable<br>/x <path>xref.file Enables/sets path</path>                              |

| У      | Disabled | Enable/Disable extended instruction set.<br>/y Enable<br>/y+ Enable<br>/y- Disable<br>Can only be enabled for processors which support the extended instruction set and |

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

#### **Command Shell Interface**

The MPASM assembler command shell interface displays a screen in Text Graphics mode. It is invoked by executing mpasm.exe in Windows Explorer.

On this screen, you can fill in the name of the source file you want to assemble and other information.

#### FIGURE: TEXT GRAPHICS MODE DISPLAY

| Source        |                                               | (c)1993-2003 Microchip Technology Inc./Byte Craft Li              |                                                                           |                                                                                                                                                 |  |

|---------------|-----------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Jource        | File                                          |                                                                   | *.ASM                                                                     |                                                                                                                                                 |  |

| Processor     | Т уре                                         |                                                                   | None                                                                      |                                                                                                                                                 |  |

| Error         | File                                          |                                                                   | Yes                                                                       |                                                                                                                                                 |  |

| oss Reference | File                                          |                                                                   | No                                                                        |                                                                                                                                                 |  |

| Listing       | File                                          |                                                                   | Yes                                                                       |                                                                                                                                                 |  |

| Hex Dump      | Т уре                                         |                                                                   | I NHX8M                                                                   | .HEX                                                                                                                                            |  |

| ble to Object | File                                          |                                                                   | No                                                                        |                                                                                                                                                 |  |

|               | Error<br>oss Reference<br>Listing<br>Hex Dump | Error File<br>oss Reference File<br>Listing File<br>Hex Dump Type | Error File :<br>oss Reference File :<br>Listing File :<br>Hex Dump Type : | Processor Type : None<br>Error File : Yes<br>oss Reference File : No<br>Listing File : Yes<br>Hex Dump Type : INHX8M<br>ble to Object File : No |  |

#### **Source File**

Type the name of your source file. The name can include a DOS path and wild cards. If you use wild cards (one of \* or ?), a list of all matching files is displayed for you to select from. To automatically enter \* . ASM in this field, press **<TAB>**.

#### **Processor Type**

If you do not specify the processor in your source file, use this field to select the processor. Enter the field by using the arrow keys, then toggle through the processors by pressing **<RET>**.

#### **Error File**

An error file (<sourcename>.err) is created by default. To turn the error file off, use the < $\tilde{A}>$  to move to the YES and press <**RET**> to change it to NO. The error filename can be changed by pressing the **<TAB**> key to move to the shaded area and typing a new name. Wild cards are not allowed in the error filename.

#### **Cross Reference File**

A cross reference file (<sourcename>.xrf) is not generated by default. To create a cross reference file, use the keyboard arrow keys to move to the NO and press <**RET**> to change it to YES. The cross reference filename can be changed by pressing the <**TAB**> key to move to the shaded area and typing a new name. Wild cards are not allowed in the cross reference filename.

#### **Listing File**

A listing file (<sourcename>.lst) is created by default. To turn the listing file off, use the <Ã> to move to the YES and press <RET> to change it to NO. The listing filename can be changed by pressing the <TAB> key to move to the shaded area and typing a new name. Wild cards are not allowed in the listing filename.

### **HEX Dump Type**

Set this value to generate the desired hex file format. Changing this value is accomplished by moving to the field with the  $<\tilde{A}>$  key and pressing the **<RET>** key to scroll through the available options. To change the hex filename, press the **<TAB>** key to move the shaded area, and type in the new name.

#### **Assemble to Object File**

Enabling this option will generate the relocatable object code that can be input to the linker and suppress generation of the hex file. The filename may be modified in the same manner as the error file.

### **Windows Shell Interface**

MPASM assembler for Windows provides a graphical interface for setting assembler options. It is invoked by executing mpasmwin.exe in Windows Explorer.

#### FIGURE: MPASM ASSEMBLER WINDOWS SHELL INTERFACE

Select a source file by typing in the name or using the **Browse** button. Set the various options as described below. Then click **Assemble** to assemble the source file.

**Note:** When MPASM assembler for Windows is invoked through MPLAB IDE, the options screen is not available. Refer to the Make Setup option in the *MPLAB IDE User's Guide* for selecting assembly options in MPLAB IDE.

| Option                   | Usage                                                                                    |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Radix                    | Override any source file radix settings.                                                 |  |  |  |

| Warning Level            | Override any source file message level settings.                                         |  |  |  |

| Hex Output               | Override any source file hex file format settings.                                       |  |  |  |

| Generated Files          | Enable/disable various output files.                                                     |  |  |  |

| Case Sensitivity         | Enable/disable case sensitivity.                                                         |  |  |  |

| Macro Expansion          | Override any source file macro expansion settings.                                       |  |  |  |

| Processor                | Override any source file processor settings.                                             |  |  |  |

| Tab Size                 | Set the list file tab size.                                                              |  |  |  |

| Extra Options            | Any additional command line options. See <u>Command Line Interface</u> for more details. |  |  |  |

| Save Settings on<br>Exit | Save these settings in mplab.ini. They will be used the next time you run mpasmwin.exe.  |  |  |  |

| Extended Mode            | Enable extended mode.                                                                    |  |  |  |

#### Microchip Technology Inc.

<u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

## Troubleshooting

If you are using **mpasm**. **exe** and get a message saying that you have run out of environment space, use Microsoft Windows Internet Explorer to select the **mpasm**. **exe** file in the MPLAB IDE installation directory, and click on the right mouse button to bring up the Properties dialog.

#### FIGURE: PROPERTIES DIALOG - MPASM.EXE

| General Program Font Memory Conventional memory                                                                                                                                                                         | Summary | Compatibility                                                                                                                          | Misc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Screen                                                                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Conventional memory                                                                                                                                                                                                     | Memory  | Font                                                                                                                                   | Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | General                                                                                                |  |

| Convertional memory   Total:   Auto   Protected   256   512   Expanded (EMS) memory   Total:   None   1280   1536   1792   Extended (XMS) memory   Total:   0   2560   2816   3072   3284   3824   3840   Total:   Auto |         | environment: Auto<br>256<br>512<br>768<br>1024<br>1280<br>1536<br>1792<br>2048<br>2304<br>2560<br>2816<br>3072<br>3328<br>3328<br>3840 | IS) memory<br>S) memory | Total: Auto<br>Pro<br>Expanded (EM<br>Total: None<br>Extended (XM<br>Total: 0<br>V Use<br>MS-DOS prote |  |

Increase the size of the Initial Environment. Usually a setting of 2048 will suffice, but if you have a lot of applications that set variables and add to your path statement in your AUTOEXEC.BAT file, you may need to make it larger.

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | >                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| and the second se | and the second second second |

# **Directives**

Directives are assembler commands that appear in the source code but are not translated directly into opcodes. They are used to control the assembler: its input, output, and data allocation.

Many of the assembler directives have alternate names and formats. These may exist to provide backward compatibility with previous assemblers from Microchip and to be compatible with individual programming practices. If portable code is desired, it is recommended that programs be written using the specifications contained here.

**Note:** Although MPASM assembler is often used with MPLINK object linker, MPASM assembler directives are not supported by MPLINK linker. See MPLINK object linker documentation for more information on linker options to control listing and hex file output.

Directives discussed are:

**Note:** Directives are not case-sensitive, e.g., cblock may be executed as CBLOCK, cblock, Cblock, etc

- \_\_BADRAM Identify Unimplemented RAM

- <u>BADROM Identify Unimplemented ROM</u>

- \_\_\_CONFIG Set Processor Configuration Bits

- \_\_IDLOCS Set Processor ID Locations

- \_\_\_MAXRAM Define Maximum RAM Location

- \_\_\_MAXROM Define Maximum ROM Location

- #DEFINE Define a Text Substitution Label

- #INCLUDE Include Additional Source File

- <u>#UNDEFINE Delete a Substitution Label</u>

- BANKISEL Generate Indirect Bank Selecting Code

- BANKSEL Generate Bank Selecting Code

- <u>CBLOCK Define a Block of Constants</u>

- <u>CODE Begin an Object File Code Section</u>

- <u>CODE\_PACK Begin an Object File Packed Code Section</u>

- <u>CONSTANT Declare Symbol Constant</u>

- DA Store Strings in Program Memory

- Data Create Numeric and Text Data

- DB Declare Data of One Byte

- DE Declare EEPROM Data Byte

- <u>DT Define Table</u>

- DW Declare Data of One Word

- ELSE Begin Alternative Assembly Block to IF

- END End Program Block

- ENDC End an Automatic Constant Block

- ENDIF End Conditional Assembly Block

- ENDM End a Macro Definition

- ENDW End a While Loop

- EQU Define an Assembler Constant

- ERROR Issue an Error Message

- ERRORLEVEL Set Message Level

- EXITM Exit from a Macro

- EXPAND Expand Macro Listing

- EXTERN Declare an Externally Defined Label

- FILL Specify Memory Fill Value

- GLOBAL Export a Label

- IDATA Begin an Object File Initialized Data Section

- IF Begin Conditionally Assembled Code Block

- IFDEF Execute If Symbol has Been Defined

- IFNDEF Execute If Symbol has not Been Defined

- LIST Listing Options

- LOCAL Declare Local Macro Variable

- MACRO Declare Macro Definition

- MESSG Create User Defined Message

- NOEXPAND Turn off Macro Expansion

- NOLIST Turn off Listing Output

- ORG Set Program Origin

- PAGE Insert Listing Page Eject

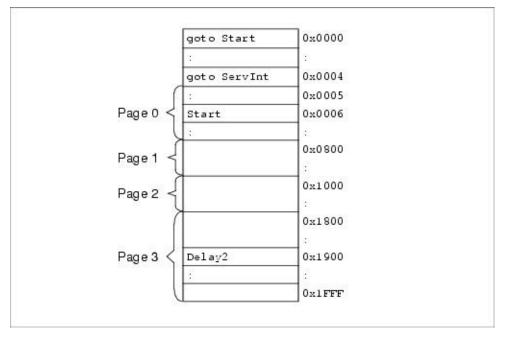

- PAGESEL Generate Page Selecting Code

- PROCESSOR Set Processor Type

- RADIX Specify Default Radix

- <u>RES Reserve Memory</u>

- SET Define an Assembler Variable

- SPACE Insert Blank Listing Lines

- SUBTITLE Specify Program Subtitle

- TITLE Specify Program Title

- UDATA Begin an Object File Uninitialized Data Section

- UDATA\_ACS Begin an Object File Access Uninitialized Data

Section

- <u>UDATA\_OVR Begin an Object File Overlayed Uninitialized Data</u>

<u>Section</u>

- <u>UDATA\_SHR Begin an Object File Shared Uninitialized Data</u>

<u>Section</u>

- VARIABLE Declare Symbol Variable

- WHILE Perform Loop While Condition is True

# **\_BADRAM - Identify Unimplemented RAM**

**Note:** badram is preceded by two underline characters, with no space in between these characters. A space is added here for readibility only.

#### **Syntax**

\_\_badram <expr>[-<expr>][, <expr>[-<expr>]]

#### Description

The \_ \_maxram and \_ \_badram directives together flag accesses to unimplemented registers. \_ \_badram defines the locations of invalid RAM addresses. This directive is designed for use with the \_ \_maxram directive. A \_ \_maxram directive must proceed any \_ \_badram directive. Each <expr> must be less than or equal to the value specified by \_ \_maxram. Once the \_ \_maxram directive is used, strict RAM address checking is enabled, using the RAM map specified by \_ \_badram. To specify a range of invalid locations, use the syntax <minloc> -<maxloc>.

#### **Example**

See the example for \_ \_maxram.

#### See Also

\_\_<u>MAXRAM</u>

# **\_BADROM - Identify Unimplemented ROM**

**Note:** badrom is preceded by two underline characters, with no space in between these characters. A space is added here for readibility only.

#### **Syntax**

\_\_badrom <expr>[-<expr>][, <expr>[-<expr>]]

#### Description

The \_\_\_\_maxrom and \_\_\_badrom directives together flag accesses to unimplemented registers. \_\_\_badrom defines the locations of invalid ROM addresses. This directive is designed for use with the \_\_\_\_maxrom directive. A \_\_\_maxrom directive must proceed any \_\_\_badrom directive. Each <expr> must be less than or equal to the value specified by \_\_\_\_maxrom. Once the \_\_\_\_\_ \_maxrom directive is used, strict ROM address checking is enabled, using the ROM map specified by \_\_\_\_badrom. To specify a range of invalid locations, use the syntax <minloc> -<maxloc>.

Specifically, a warning will be raised in the following circumstances:

- the target of a G0T0 or CALL instruction is evaluated by the assembler to a constant, and falls in a bad ROM region

- the target of an LGOTO or LCALL psuedo-op is evaluated by the assembler to a constant, and falls in a bad ROM region

• a . hex file is being generated, and part of an instruction falls in a bad ROM region

# Example

See the example for \_ \_maxrom.

#### See Also

Microchip Technology Inc.

<u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

#### \_\_CONFIG - Set Processor Configuration Bits

**Note: config** is preceded by two underline characters, with no space in between these characters. A space is added here for readability only.

### **Syntax**

\_\_config <expr> OR \_\_config <addr>, <expr>

# Description

Sets the processor's configuration bits to the value described by <expr>. For PIC18CXXX devices, the address of a valid configuration byte must also be specified by <addr>. Refer to individual PICmicro microcontroller data sheets for a description of the configuration bits.

Before this directive is used, the processor must be declared through the command line, the list directive, or the processor directive. If this directive is used with the PIC17CXXX family, the Hex file output format must be set to INHX32 through the command line or the list directive.

### Examples

#### example 1:

list p=17c42,f=INHX32 ;define processor and select output format \_\_\_\_config H'FFFF' ;default configuration bits

#### example 2:

list p=16f877a ;list directive to define processor

#include <p16f877a.inc> ;include file with config bit definitions

\_\_\_config \_HS\_OSC & \_WDT\_OFF & \_LVP\_OFF ;Set oscillator to HS,

;watchdog time off,

;low-voltage prog. off

#### example 3:

list p=18f8720 ;list directive to define processor #include <p18f8720.inc> ;include file with config bit definitions \_\_CONFIG \_CONFIG1H, \_OSCS\_OFF\_1H & \_HS\_OSC\_1H ;Set osc info \_\_CONFIG \_CONFIG2L, \_BOR\_OFF\_2L & \_PWRT\_OFF\_2L ;Set power info

#### See Also

\_\_\_\_IDLOCS LIST PROCESSOR

### **\_IDLOCS - Set Processor ID Locations**

**Note:** idlocs is preceded by two underline characters, with no space in between these characters. A space is added here for readibility only.

#### **Syntax**

\_\_idlocs <expr> or \_\_idlocs <expr1>, <expr2>

#### Description

For PIC12CXXX and PIC16CXXX devices, \_\_\_idlocs sets the four ID locations to the hexadecimal value of <expr>. For PIC18CXXX devices, \_\_\_idlocs sets the two-byte device ID <expr1> to the hexadecimal value of <expr2>. This directive is not valid for the PIC17CXXX family.

For example, if <expr> evaluates to 1AF, the first (lowest address) ID location is zero, the second is one, the third is ten, and the fourth is fifteen.

Before this directive is used, the processor must be declared through the command line, the list directive, or the processor directive.

#### Example

\_\_idlocs H'1234'

#### See Also

<u>CONFIG LIST PROCESSOR</u>

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

#### \_\_MAXRAM - Define Maximum RAM Location

**Note:** maxram is preceded by two underline characters, with no space in between these characters. A space is added here for readibility only.

#### **Syntax**

\_\_maxram <expr>

#### Description

The \_\_\_\_maxram and \_\_\_\_badram directives together flag accesses to unimplemented registers. \_\_\_\_maxram defines the absolute maximum valid RAM address and initializes the map of valid RAM addresses to all addresses valid at and below <expr>. <expr> must be greater than or equal to the maximum page 0 RAM address and less than 1000H. This directive is designed for use with the \_\_\_\_badram directive. Once the \_\_\_\_maxram directive is used, strict RAM address checking is enabled, using the RAM map specified by \_\_\_\_badram.

\_\_\_\_maxram can be used more than once in a source file. Each use redefines the maximum valid RAM address and resets the RAM map to all locations.

#### Example

list p=16c622 \_\_maxram H'0BF' \_\_badram H'07'-H'09', H'0D'-H'1E' \_\_badram H'87'-H'89', H'8D', H'8F'-H'9E' movwf H'07' ; Generates invalid RAM warning movwf H'87' ; Generates invalid RAM warning ; and truncation message

#### See Also

\_\_BADRAM

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200

Voice: (480) 792-7200 Fax: (480) 899-9210 Microchip's E-mail Address

#### \_\_MAXROM - Define Maximum ROM Location

**Note:** maxrom is preceded by two underline characters, with no space in between these characters. A space is added here for readibility only.

## **Syntax**

\_\_maxrom <expr>

# Description

The \_ \_maxrom and \_ \_badrom directives together flag accesses to unimplemented registers. \_ \_maxrom defines the absolute maximum valid ROM address and initializes the map of valid ROM addresses to all addresses valid at and below <expr>. <expr> must be greater than or equal to the maximum ROM address of the target device. This directive is designed for use with the \_ \_badrom directive. Once the

\_\_maxrom directive is used, strict ROM address checking is enabled, using the ROM map specified by \_\_badrom.

\_\_\_\_\_maxrom can be used more than once in a source file. Each use redefines the maximum valid ROM address and resets the ROM map to all locations.

### Example

list p=12c508 \_\_maxrom 0x1FF \_\_badrom 0x2 - 0x4, 0xA org 0x5 goto 0x2 ; generates a warning call 0x3 ; generates a warning org 0xA movlw 5; generates a warning

#### **See Also**

BADROM

#### **#DEFINE - Define a Text Substitution Label**

#### **Syntax**

```

#define <name> [<string>]

```

# Description

This directive defines a text substitution string. Wherever <name> is encountered in the assembly code, <string> will be substituted.

Using the directive with no <string> causes a definition of <name> to be noted internally and may be tested for using the ifdef directive.

This directive emulates the ANSI 'C' standard for **#define**. Symbols defined with this method are not available for viewing using MPLAB IDE.

#### Example

```

#define length 20

#define control 0x19,7

#define position(X,Y,Z) (Y-(2 * Z +X))

:

:

test_label dw position(1, length, 512)

bsf control ; set bit 7 in f19

```

#### See Also

#### **#UNDEFINE #INCLUDE IFDEF IFNDEF**

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

#### **#INCLUDE - Include Additional Source File**

#### **Syntax**

#include <<include\_file>>

#include "<include\_file>"

## Description

The specified file is read in as source code. The effect is the same as if the entire text of the included file were inserted into the file at the location of the include statement. Upon end-of-file, source code assembly will resume from the original source file. Up to 5 levels of nesting are permitted. Up to 255 include files are allowed.

<include\_file> may be enclosed in quotes or angle brackets. If a fully qualified path is specified, only that path will be searched. Otherwise, the search order is: current working directory, source file directory, MPASM assembler executable directory.

#### Example

#include "c:\sys\sysdefs.inc" ; system defs

#include <regs.h> ; register defs

#### See Also

#### <u>#DEFINE</u> <u>#UNDEFINE</u>

#### **#UNDEFINE - Delete a Substitution Label**

#### **Syntax**

#undefine <label>

# Description

label> is an identifier previously defined with the #define directive. It must be a valid MPASM assembler label. The symbol named is removed from the symbol table.

#### Example

#define length 20

:

#undefine length

#### See Also

**#DEFINE #INCLUDE IFDEF IFNDEF**

#### BANKISEL - Generate Indirect Bank Selecting Code

#### **Syntax**

bankisel <label>

# Description

For use when generating an object file. This directive is an instruction to the linker to generate the appropriate bank selecting code for an indirect access of the address specified by <label>. Only one <label> should be specified. No operations can be performed on <label>. <label> must have been previously defined.

The linker will generate the appropriate bank selecting code. For 14-bit core devices, the appropriate bit set/clear instruction on the IRP bit in the STATUS register will be generated. For the 16-bit core devices, MOVLB or MOVLR will be generated. If the user can completely specify the indirect address without these instructions, no code will be generated.

For more information, refer to <u>Relocatable Objects</u>.

# Example

movlw Var1 movwf FSR bankisel Var1 : movwf INDF

#### **See Also**

#### **BANKSEL PAGESEL**

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

\_

#### **BANKSEL - Generate Bank Selecting Code**

#### **Syntax**

banksel <label>

#### Description

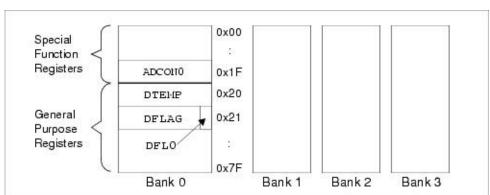

For use when generating an object file. This directive is an instruction to the linker to generate bank selecting code to set the bank to the bank containing the designated <label>. Only one <label> should be specified. No operations can be performed on <label>. <label> must have been previously defined.

The linker will generate the appropriate bank selecting code. For 12-bit core devices, the appropriate bit set/clear instructions on the FSR will be generated. For 14-bit devices, bit set/clear instructions on the STATUS register will be generated. For the 16-bit core devices, MOVLB or MOVLR will be generated. For the enhanced 16-bit core devices, MOVLB will be generated. If the device contains only one bank of RAM, no instructions will be generated.

For more information, refer to <u>Relocatable Objects</u>.

#### Example

banksel Var1 movwf Var1

#### See Also

BANKISEL PAGESEL

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

### **CBLOCK - Define a Block of Constants**

#### **Syntax**

```

cblock [<expr>]

<label>[:<increment>][,<label>[:<increment>]]

endc

```

## Description

Define a list of named constants. Each <label> is assigned a value of one higher than the previous <label>. The purpose of this directive is to assign address offsets to many labels. The list of names end when an endc directive is encountered.

<expr> indicates the starting value for the first name in the block. If no expression is found, the first name will receive a value one higher than the final name in the previous cblock. If the first cblock in the source file has no <expr>, assigned values start with zero.

If <increment> is specified, then the next <label> is assigned the value of <increment> higher than the previous <label>.

Multiple names may be given on a line, separated by commas.

cblock is useful for defining constants in program and data memory.

### Example

cblock 0x20 ; name\_1 will be assigned 20 name\_1, name\_2 ; name\_2, 21 and so on

name\_3, name\_4 ; name\_4 is assigned 23. endc cblock 0x30 TwoByteVar: 0, TwoByteHigh, TwoByteLow Queue: QUEUE\_SIZE QueueHead, QueueTail Double1:2, Double2:2 endc

#### See Also

**ENDC**

Microchip Technology Inc.

<u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

### **CODE - Begin an Object File Code Section**

#### **Syntax**

[<label>] code [<ROM address>]

# Description

For use when generating an object file. Declares the beginning of a section of program code. If <label> is not specified, the section is named . code. The starting address is initialized to the specified address or will be assigned at link time if no address is specified.

Note: Two sections in the same source file may not have the same name.

For more information, refer to <u>Relocatable Objects</u>.

### Example

RESET code H'01FF' goto START

#### See Also

EXTERN CODE\_PACK GLOBAL IDATA UDATA\_ACS UDATA\_OVR UDATA\_SHR

#### CODE\_PACK - Begin an Object File Packed Code Section

#### **Syntax**

[<label>] code\_pack [<ROM address>]

# Description

For use when generating an object file. Declares the beginning of a section of program code or ROM data where a padding byte of zero is not appended to an odd number of bytes. If <label> is not specified, the section is named . Code. The starting address is initialized to <ROM address> or will be assigned at link time if no address is specified. If <ROM address> is specified, it must be word-aligned.

Note: Two sections in the same source file may not have the same name

For more information, refer to <u>Relocatable Objects</u>.

Note: This directive is only available for the PIC18 family of devices.

#### Example

00001 LIST P=18Cxx 00002 00003 packed code\_pack H'1F0' 0001F0 01 02 03 00004 DB 1, 2, 3 0001F3 04 05 00005 DB 4, 5 00006 00007 padded code 000000 0201 0003 00008 DB 1, 2, 3 000004 0504 00009 DB 4, 5 00010 00011 END

#### See Also

EXTERN CODE GLOBAL IDATA UDATA UDATA\_ACS UDATA\_OVR UDATA\_SHR

# **CONSTANT - Declare Symbol Constant**

# **Syntax**

constant <label>=<expr> [...,<label>=<expr>]

# Description

Creates symbols for use in MPASM assembler expressions. Constants may not be reset after having once been initialized, and the expression must be fully resolvable at the time of the assignment. This is the principal difference between symbols declared as constant and those declared as variable, or created by the set directive. Otherwise, constants and variables may be used interchangeably in expressions.

### Example

```

variable RecLength=64 ; Set Default

; RecLength

constant BufLength=512 ; Init BufLength

. ; RecLength may

```

.; be reset later

```

.; in RecLength=128

```

.;

constant MaxMem=RecLength+BufLength ;CalcMaxMem

### See Also

SET VARIABLE

Microchip Technology Inc.

<u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

### **DA - Store Strings in Program Memory**

#### **Syntax**

[<label>] da <expr> [, <expr2>, ..., <exprn>]

# Description

Generates a packed 14-bit number representing two 7-bit ASCII characters. This is useful for storing strings in memory for the PICmicro MCU Flash ROM devices.

#### Examples

• da "abcdef"

will put 30E2 31E4 32E6 3380 into program memory

• da "12345678" ,0

will put 18B2 19B4 1AB6 0000 into program memory

• da 0xFFFF

will put 0x3FFF into program memory

#### **Data - Create Numeric and Text Data**

#### **Syntax**

[<label>] data <expr>,[,<expr>,...,<expr>]

[<label>] data "<text\_string>"[,"<text\_string>",...]

### Description

Initialize one or more words of program memory with data. The data may be in the form of constants, relocatable or external labels, or expressions of any of the above. The data may also consist of ASCII character strings, <text\_string>, enclosed in single quotes for one character or double quotes for strings. Single character items are placed into the low byte of the word, while strings are packed two to a word. If an odd number of characters are given in a string, the final byte is zero. On all families except the PIC18CXXX, the first character is in the most significant byte of the word. On the PIC18CXXX, the first character is in the least significant byte of the word.

When generating an object file, this directive can also be used to declare initialized data values. Refer to the *idata* directive for more information.

#### Example

data reloc\_label+10 ; constants

data 1,2,ext\_label ; constants, externals

data "testing 1,2,3" ; text string

data 'N' ; single character

data start\_of\_program ; relocatable label

#### **See Also**

#### <u>DB DE DT DW IDATA</u>

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 Microchip's E-mail Address

\_

#### **DB - Declare Data of One Byte**

#### **Syntax**

[<label>] db <expr>[,<expr>,...,<expr>]

# Description

Reserve program memory words with packed 8-bit values. Multiple expressions continue to fill bytes consecutively until the end of expressions. Should there be an odd number of expressions, the last byte will be zero.

When generating an object file, this directive can also be used to declare initialized data values. Refer to the *idata* directive for more information.

#### Example

db 't', 0x0f, 'e', 0x0f, 's', 0x0f, 't', '\n'

#### See Also

DATA DE DT DW IDATA

#### **DE - Declare EEPROM Data Byte**

#### **Syntax**

[<label>] de <expr> [, <expr>, ..., <expr>]

#### Description

Although designed for initializing EEPROM data on the PIC16F8X, the directive can be used at any location for any processor.

#### PIC18XXXX

Reserve memory word bytes are packed.

When using **de**, make sure to specify the start of data memory at 0xF00000 for use with programmers.

#### **Other PICmicro's**

Reserve memory words with 8-bit data. Each  $\langle expr \rangle$  must evaluate to an 8-bit value. The upper bits of the program word are zeroes. Each character in a string is stored in a separate word.

When using **de**, make sure to specify the start of data memory at 0x2100 for use with programmers.

#### Example

org H'2100' ; Initialize EEPROM Data de "My Program, v1.0", 0

#### DATA DB DT DW

Microchip Technology Inc. <u>Microchip's Web Site</u> Voice: (480) 792-7200 Fax: (480) 899-9210 <u>Microchip's E-mail Address</u>

-

#### **DT - Define Table**

### **Syntax**

[<label>] dt <expr> [, <expr>, ..., <expr>]

# Description

Generates a series of RETLW instructions, one instruction for each <expr>. Each <expr> must be an 8-bit value. Each character in a string is stored in its own RETLW instruction.

#### Example

dt "A Message", 0 dt FirstValue, SecondValue, EndOfValues

#### See Also

DATA DB DE DW

#### **DW - Declare Data of One Word**

#### **Syntax**

[<label>] dw <expr>[,<expr>,...,<expr>]

# Description

Reserve program memory words for data, initializing that space to specific values. For PIC18CXXX devices, dw functions like db. Values are stored into successive memory locations and the location counter is incremented by one. Expressions may be literal strings and are stored as described in the data directive.

When generating an object file, this directive can also be used to declare initialized data values. Refer to the *idata* directive for more information.

#### Example

dw 39, "diagnostic 39", (d\_list\*2+d\_offset) dw diagbase-1

#### See Also

DATA DB IDATA

# ELSE - Begin Alternative Assembly Block to IF

#### **Syntax**

else

#### Description

Used in conjunction with an if directive to provide an alternative path of assembly code should the if evaluate to false. else may be used inside a regular program block or macro.

#### Example

speed macro rate if rate < 50 dw slow else dw fast endif endm

#### See Also

ENDIF IF

< >

#### **END - End Program Block**

### **Syntax**

end

#### Description

Indicates the end of the program.

#### Example

list p=17c42

: ; executable code

: ;

end ; end of instructions

#### See Also

#### <u>ORG</u>

#### Microchip Technology Inc.

Microchip's Web Site Voice: (480) 792-7200 Fax: (480) 899-9210 Microchip's E-mail Address

#### **ENDC - End an Automatic Constant Block**

#### **Syntax**

endc

#### Description

endc terminates the end of a cblock list. It must be supplied to terminate the list.

#### See Also

**CBLOCK**

#### **ENDIF - End Conditional Assembly Block**

#### **Syntax**

endif

#### Description

This directive marks the end of a conditional assembly block. endif may be used inside a regular program block or macro.

#### See Also

ELSE IF

#### **ENDM - End a Macro Definition**

#### **Syntax**

endm

### **Description**

Terminates a macro definition begun with macro.

#### Example

make\_table macro arg1, arg2 dw arg1, 0; null terminate table name res arg2; reserve storage endm

#### See Also

MACRO EXITM

#### Microchip Technology Inc. Microchip's Web Site Voice: (480) 792-7200 Fax: (480) 899-9210

Microchip's E-mail Address

#### **ENDW - End a While Loop**

#### **Syntax**

endw

#### Description

endw terminates a while loop. As long as the condition specified by the while directive remains true, the source code between the while directive and the endw directive will be repeatedly expanded in the assembly source code stream. This directive may be used inside a regular program block or macro.

#### Example

See the example for WHILE.

#### See Also

<u>WHILE</u>

#### **EQU - Define an Assembler Constant**

#### **Syntax**

<label> equ <expr>

#### Description

The value of <expr> is assigned to <label>.

#### Example

four equ 4 ; assigned the numeric value of 4 to label four

#### See Also

<u>SET</u>

#### **ERROR - Issue an Error Message**

#### **Syntax**

error "<text\_string>"